Siインターポーザを樹脂基板に変更した低コスト版の「CoWoS」:福田昭のデバイス通信(337) TSMCが開発してきた最先端パッケージング技術(10)(2/2 ページ)

樹脂基板の再配線層をインターポーザに

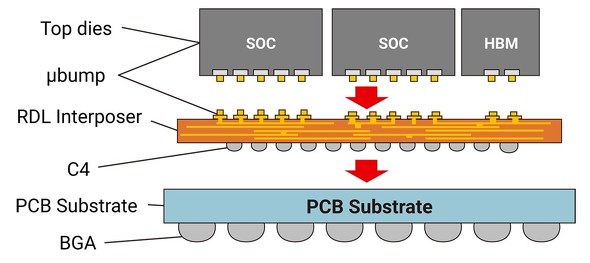

始めは「CoWoS_R(RDL Interposer)」の概要を説明しよう。「CoWoS_R」はSiインターポーザの代わりに、樹脂基板の再配線層(RDL)をインターポーザに利用する。RDLインターポーザの上に載るシリコンダイとの間は、マイクロバンプで接続する。RDLインターポーザとパッケージ基板との間は、C4バンプでつなぐ。パッケージ基板は通常、BGAタイプである。

RDLインターポーザは6層の銅配線と高分子絶縁材料によってシリコンダイ間とシリコンダイ-パッケージ基板間を接続する。銅配線の幅/間隔は2μm/2μmとかなり狭い。6層の銅配線は、信号線の両隣を接地線で囲んだ回路(コプレーナ線路)にする、中間の配線層を接地面(グラウンドプレーン)とする、といった工夫によって信号品質と電源品質を確保している。

小さなシリコン基板を埋め込んでダイ間の広帯域高密度接続を実現

続いて「CoWoS_L(Local Silicon Interconnect + RDL Inerposer)」である。インターポーザの材料はモールド樹脂であり、モールド樹脂の両面に比較的広い配線幅のRDLを設けてある。またモールド樹脂を貫通するビア(TIV:Through Interposer Via)によって表裏間で信号と電源系を接続する。

広帯域高密度のシリコンダイ間接続は、サブミクロン寸法の高密度な多層銅配線を形成した小さなシリコン基板「シリコンブリッジ」が担う。シリコンブリッジは、モールド樹脂インターポーザで2つのダイが隣接している部分に埋め込む。

「CoWoS_L(Local Silicon Interconnect + RDL Inerposer)」の構造例。左はレイアウトと「シリコンブリッジ(LSI:Local Silicon Interconnect)」の位置(点線部分)。ASICとHBMの接続にシリコンブリッジを利用する。右は断面構造例[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「CoWoS_L(Local Silicon Interconnect + RDL Inerposer)」の構造例。左はレイアウトと「シリコンブリッジ(LSI:Local Silicon Interconnect)」の位置(点線部分)。ASICとHBMの接続にシリコンブリッジを利用する。右は断面構造例[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)モールド樹脂に埋め込む小さなシリコン基板にはほかに、「IPD(Integrated Passive Device)」と呼ぶ、受動素子アレイを高密度に作り込んだ基板がある。IPDをASICダイあるいはSoCダイの直下にレイアウトすることで、信号品質を高めたり、電源電圧変動を抑制したりする。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増