チップレットの普及拡大へ、「UCIe 1.0」が登場:Intelなど10社が業界団体も設立(2/2 ページ)

標準規格の必要性

しかし、チップレットのおかげで柔軟性が向上するということは、メーカー各社のチップレット設計手法がそれぞれに異なるということを意味する。UCIe 1.0標準規格が導入される以前は、OCP(Open Compute Project)が、物理インタフェース規格であるODSA(Open Domain-Specific Architecture)のサブプロジェクトにおいて、チップレットを組み立てるための一般的なプロセスを確立すべく、ベストプラクティスをまとめる作業を進めていた。

もう1つ、チップレットエコシステムの明確化を目指すメーカーの例として挙げられるのが、コンピュータハードウェアメーカーであるzGlueだ。同社は、カスタムチップを構築するためのプラットフォームおよびプロセスをオンデマンドで提供することにより、ハードウェアメーカー各社が市場投入までの時間短縮を求める圧力の高まりに対応できるよう、サポートを提供している。

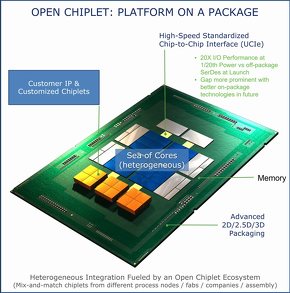

UCIe 1.0規格も、それと同様の目標を掲げている。半導体業界全体を、オープンプラットフォームを中心として連携させることにより、ヘテロジニアスインテグレーションをサポート可能な、チップレットベースのソリューションの実現を目指していく。これにより、プロセスノードや工場、ベンダーなどがさまざまに異なる多様なチップレットに対して、柔軟性を維持できるようになるのだ。

Das Sharma氏は、「チップレットのヘテロジニアスインテグレーションは、幅広い規模の経済を実現する上で必要である。既存のチップレットを再利用することで、市場投入までの時間短縮が可能になる」と述べる。

UCIe 1.0規格は、ダイ間の物理層やプロトコルスタック、ソフトウェアモデル、コンプライアンステストなどのインターコネクトを完全に標準化することが実証されている。このためエンドユーザーは、マルチベンダーエコシステムのコンポーネントを組み合わせてSoC構築を実現することが可能になる。「UCIe 1.0規格は、業界全体に大変革をもたらし、メーカー独自のSoCを構築するための方法として採用されるだろう」(Das Sharma氏)

さらに同氏は、「UCIeコンソーシアムの目標は、UCIe 1.0規格が強制力や性能、コスト特性を確実に提供できるようにすることだ。電力効率に優れた方法で、高帯域幅を提供できるようにしていきたい。そうすれば、超低レイテンシかつ高コスト効率、低消費電力で、幅広い帯域幅を提供可能なシステムを構築できるようになる」と説明する。

同氏は、「物事の機能の仕方を明示可能な、相互運用性も重要である。われわれとしては、フルスタックを確実に定義したい考えだ。もしプラグアンドプレイを採用する場合は、また一から作り直すことは避けたいため、既存のソフトウェアを利用するつもりだ」と述べている。

CXL/PCIe規格は、ボードツーボードインタフェースであり、汎用ユースケースに対応可能なため、プロトコルとして選定されている。PCIe/CXL.ioはI/Oアタッチを、CXL.memはメモリユースケースを、そしてCXL.cacheはアクセラレーターユースケースを扱う。PCIeやCXLと同様に、UCIeも相互運用性に焦点を当てていく。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

今回は、「IEDM2020」から先端パッケージの講演をいくつか紹介する。そこで見えてきたのは、今後「ムーアの法則」のけん引役となるかもしれない「チップレット」技術と、その開発競争が進んでいるということだった。 「ムーアの法則」減速への打開策? ヘテロジニアス設計

「ムーアの法則」減速への打開策? ヘテロジニアス設計

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。 Intel、TSMCを活用しつつ「リーダーシップを取り戻す」

Intel、TSMCを活用しつつ「リーダーシップを取り戻す」

Intelが、かつてのライバルであったTSMCへの依存度を高めている。売上高を増加させ、最終的に製造規模と半導体プロセス技術分野において世界リーダーとしての優位性を取り戻していきたい考えのようだ。 チップレットが主流になるための2つの要素

チップレットが主流になるための2つの要素

現在、データセンターのワークロードが急激な進化を遂げている。計算やメモリ、IOなどの機能が変化しながら組み合わさって、より高い計算密度が求められるようになってきた。このためアーキテクチャは、従来の「One-size-fits-all」型のモノリシックなソリューションから、ディスアグリゲーション(分離)された機能へと移行が進み、特定用途向けとして個別にスケーリングすることが可能になっている。 10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編)

10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編)

今回からは、高性能コンピューティング(HPC)向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」を解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待