混載MRAMの高速読み出し/書き換え技術を開発:ルネサスが「VLSI 2022」で発表(1/2 ページ)

ルネサス エレクトロニクス(以下、ルネサス)は2022年6月16日、スピン注入磁化反転型磁気抵抗メモリ(STT-MRAM、以下MRAM)の高速読み出し/書き換え技術を開発したと発表した。同技術を適用した32MビットのMRAMメモリセルアレイを搭載したテストチップでは、150℃の接合温度でランダムアクセス時間5.9ナノ秒、書き換えスループット5.8Mバイト/秒を達成。

ルネサス エレクトロニクス(以下、ルネサス)は2022年6月16日、スピン注入磁化反転型磁気抵抗メモリ(STT-MRAM、以下MRAM)の高速読み出し/書き換え技術を開発したと発表した。同技術を適用した32MビットのMRAMメモリセルアレイを搭載したテストチップでは、150℃の接合温度でランダムアクセス時間5.9ナノ秒、書き換えスループット5.8Mバイト/秒を達成。ルネサスは「MRMA混載マイコンの実用化に向け、また一歩近づいた」とする。

なお、本技術は、2022年6月12〜17日までハワイで開催されている「2022 VLSI技術/回路シンポジウム」で発表された。

容量結合で電圧レベルを上げる

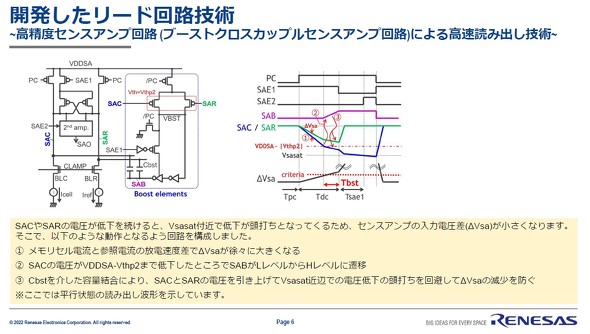

高速読み出し技術では、高精度のセンスアンプ回路によって、高速な読み出し動作を実現する。

MRAMは、磁気トンネル接合素子の高抵抗状態と低抵抗状態を、データの「1」「0」に対応させて情報を記憶し、メモリセル電流(Icell)と参照電流(Iref)による放電速度の差によって発生した電圧差を、差動センスアンプで増幅することでデータを読み分ける。だが、「1」状態と「0」状態の間のメモリセル電流差が小さくなると、センスアンプへの入力電圧差が小さくなり、読み分けにくくなってしまう。さらに、放電時間を伸ばして入力電圧差を大きくしようとすると、今度はセンスアンプへの差動入力ノードが放電しきってしまい、読み出しに必要な電圧差を確保できなくなる。

そこでルネサスは、放電中にセンスアンプの差動入力ノードの電圧レベルを検知し、容量結合によって電圧レベルを上げる回路(「Boost element」)を提案。従来のセンスアンプ回路に、同Boost element回路を追加することで、読み出しに必要な電圧差を確保できるようにした。これにより、高速かつ高精度な読み出し動作が可能になった。

従来のセンスアンプ回路に「Boost element」を追加。容量結合により、差動入力ノードの電圧レベルを上げることで、読み出しに必要な電圧差を確保する[クリックで拡大] 出所:ルネサス エレクトロニクス

従来のセンスアンプ回路に「Boost element」を追加。容量結合により、差動入力ノードの電圧レベルを上げることで、読み出しに必要な電圧差を確保する[クリックで拡大] 出所:ルネサス エレクトロニクス電圧印加時間と、書き換え動作モード間の遷移時間を短縮させる

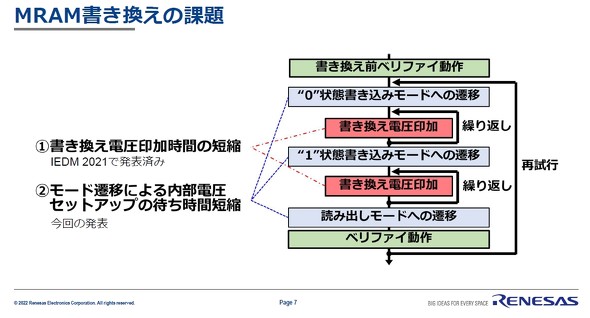

高速な書き換え技術については、1)書き換え電圧印加時間の短縮、2)書き換え動作モード間の遷移時間の短縮、の2つを開発した。

書き換えを高速化する2つの技術の概要。書き換え動作には、いくつかの動作モード(図中のブルーで示しているところ)が含まれている。これらの動作モードが遷移する際、内部電圧セットアップの待ち時間が発生するが、ルネサスは今回、この待ち時間を短縮する技術を開発した[クリックで拡大] 出所:ルネサス エレクトロニクス

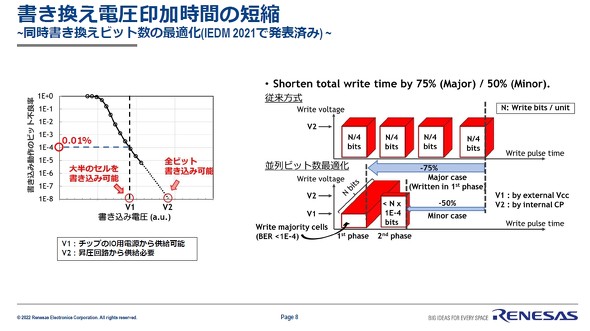

書き換えを高速化する2つの技術の概要。書き換え動作には、いくつかの動作モード(図中のブルーで示しているところ)が含まれている。これらの動作モードが遷移する際、内部電圧セットアップの待ち時間が発生するが、ルネサスは今回、この待ち時間を短縮する技術を開発した[クリックで拡大] 出所:ルネサス エレクトロニクス書き換え電圧印加時間の短縮は、2021年12月に開催された、半導体デバイス/プロセス技術の国際学会「IEDM」で発表した技術を、さらに改善したものとなる。

書き換え電圧印加時間の短縮は、ごくわずか(〜0.01%)な書き込みビット不良率を許容する代わりに、書き込み電圧を下げ、電圧印加時間を削減するというもの。

従来は、書き換え単位の全ビットを書き込むために、チャージポンプ回路で昇圧した高い書き換え電圧を印加していた。だが、チャージポンプ回路の電流供給能力には制約があるため、複数回に分けて印加する必要があった。これに対し、0.01%のビット不良率を許容すれば、チップのIO用電源から供給できる低い書き換え電圧で、ほぼ全ビットを書き換えることができる(第1段階)。その後、書き残したビット(0.01%のビット)がある場合は、これだけを、チャージポンプ回路で生成した高い書き換え電圧を印加して書き換える(第2段階)

この仕組みにより、電圧印加時間は従来に比べて、第1段階では75%、第2段階では50%、削減できるという。

ルネサスは「設計にもよるが、一般的にMRAMの書き換え単位は128ビットや256ビットなど、数十から数百ビットであることが多い。そのため、書き込みビット不良率が0.01%でも、ほとんどの場合は第1段階で書き換えることができる。第2段階まで必要になるのは、100回に1回程度の割合だ」と説明する。

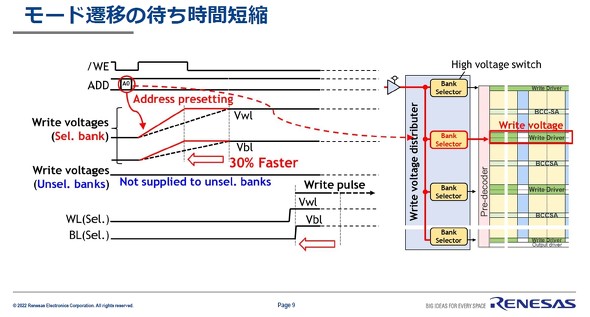

書き換え動作モード間の遷移時間は、書き換え電圧を印加する領域を絞り込むことで、短縮する。従来は、全ての領域に書き換え電圧を印加していたが、「そもそも全領域に電圧をかける必要はない」(ルネサス)。そこでルネサスは、メモリセルアレイの前段に高電圧のスイッチを設け、書き換え電圧を印加する領域を限定する技術を開発した。具体的には、書き換え電圧を立ち上げる前に、書き換え対象のアドレスをMRAMマクロに入力することで、高電圧を印加する書き込みドライバーやワード線ドライバーを絞り込む。これにより、書き換え電圧発生回路の出力の寄生容量を削減し、遷移時間を30%短縮したという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増