混載MRAMの高速読み出し/書き換え技術を開発:ルネサスが「VLSI 2022」で発表(2/2 ページ)

テストチップで5.9ナノ秒の読み出し時間を達成

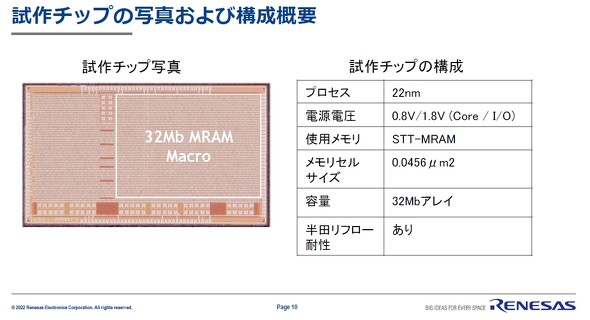

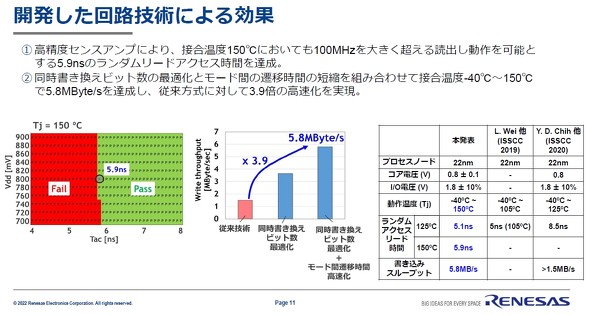

ルネサスはこれらの技術を適用し、22nmロジック混載MRAMプロセスで試作した32MビットのMRAMメモリセルアレイを搭載したテストチップを用意。このテストチップを評価したところ、最大接合温度150℃において、5.9ナノ秒のランダムリードアクセス時間を達成。書き換えスループットでは、従来方式に比べて3.9倍となる5.8Mバイト/秒を実現した。

「クロスオーバー領域」に向け、MCUのさらなる高性能化を目指す

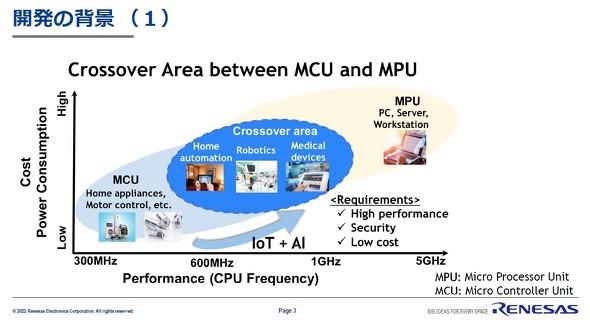

近年、IoT(モノのインターネット)やAI(人工知能)技術の進歩により、民生機器や産業機器では、より高い処理性能が求められるようになっている。その処理性能は、従来のMCUとMPUのちょうど中間に当たる領域であることから、「クロスオーバー領域」とも呼ばれる。

ルネサスは、「BOMコストが低く、従来の組み込み開発環境の資産を生かせるMCUで、このクロスオーバー領域をカバーするには、MCUのさらなる高性能化が要求される。さらに、メモリでもコスト低減は必須の要件である」と説明する。

MCUの処理性能を上げる(つまりCPUの動作周波数を上げる)には、より微細なプロセスを適用することが一般的だ。ロジックプロセスでは、7nm、5nmといった最先端プロセスが登場しているが、「不揮発メモリが混載されるプロセスの最先端は、現在ルネサスがフラッシュ混載MCUを製造している28nmが最先端である」(同社)

28nm以降の先端プロセスに混載する不揮発メモリには、前工程で形成されるフラッシュメモリよりも、配線工程で形成されるMRAMの方が、混載プロセスの開発が容易で、製造コストも安くなる。

ルネサスとしては、まずはMCUの性能を引き上げることでクロスオーバー領域をカバーする方針だ。ルネサスは現在、動作周波数が1GHz付近では、MPUである「RZ」ファミリーを展開している。一方、主要なMCUである独自コアの「RX」ファミリーやArmコアの「RA」ファミリーでは、最大周波数が240MHzや200MHzとなっている。「不揮発メモリを混載したMCUは使い勝手が優れているので、今回発表した混載MRAMの技術開発を続けながら、クロスオーバー領域に向けて、今後もMCUのさらなる高性能化を目指していく」(ルネサス)

関連記事

ルネサス、組み込みAI技術企業Reality AIを買収

ルネサス、組み込みAI技術企業Reality AIを買収

ルネサス エレクトロニクスは2022年6月9日、組み込みAIソリューションを提供するReality Analytics, Inc.(以下、Reality AI)を買収すると発表した。買収は現金で行い、2022年中に買収を完了させる予定。 ルネサスが甲府工場を再開、300mm対応でパワー半導体の生産へ

ルネサスが甲府工場を再開、300mm対応でパワー半導体の生産へ

ルネサス エレクトロニクス(以下、ルネサス)は2022年5月17日、2014年10月に閉鎖した甲府工場(山梨県甲斐市)を、300mmウエハー対応のパワー半導体生産ラインとして稼働を再開すると発表した。設備投資は900億円規模で、2024年の稼働再開を目指す。 サプライチェーン混乱も「ニューノーマル」、増収増益のルネサス

サプライチェーン混乱も「ニューノーマル」、増収増益のルネサス

ルネサス エレクトロニクスは2022年4月27日、2022年12月期(2022年度)第1四半期(1〜3月期)決算を発表した。2022年度第1四半期業績(Non-GAAPベース)は、売上高3467億円(前年同期比70.2%増)、営業利益1355億円(同829億円増)、当期純利益901億円(同575億円増)で大幅な増収増益になった。 ルネサス、ウィニング・コンビネーションを追加

ルネサス、ウィニング・コンビネーションを追加

ルネサス エレクトロニクスは、子会社のCeleno製Wi-Fiチップセットとルネサス製MCUなどを組み合わせたウィニング・コンビネーションソリューションとして、新たに10種類を発表した。 自動運転L2+/L3を普及車にも、ルネサスの「R-Car V4H」

自動運転L2+/L3を普及車にも、ルネサスの「R-Car V4H」

ルネサス エレクトロニクス(以下、ルネサス)は2022年3月8日、普及価格帯の車両にも自動運転レベル2+/レベル3を搭載可能にする車載SoC(System on Chip)「R-Car V4H」を発売した。ADAS(先進運転支援システム)や自動運転システムのメインプロセッシング用SoCで、最適なIP(Intellectual Property)の組み合わせによって、業界トップレベルの電力性能比を実現したという。同日からサンプル出荷を開始し、2024年第2四半期に量産開始予定だ。 ルネサスの汎用MPU、64ビットRISC-V コアを搭載

ルネサスの汎用MPU、64ビットRISC-V コアを搭載

ルネサス エレクトロニクスは、64ビットRISC-V CPUコアを搭載した汎用MPU「RZ/Five」のサンプル出荷を始めた。IoTエッジデバイスに向けて性能や機能を最適化している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増