AMDが開発した第4世代EPYCプロセッサのCXLメモリ拡張:福田昭のデバイス通信(376)(2/2 ページ)

初のCXL対応システムとなる第4世代EPYCサーバ

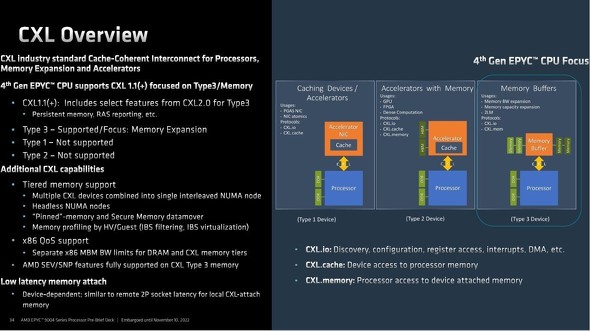

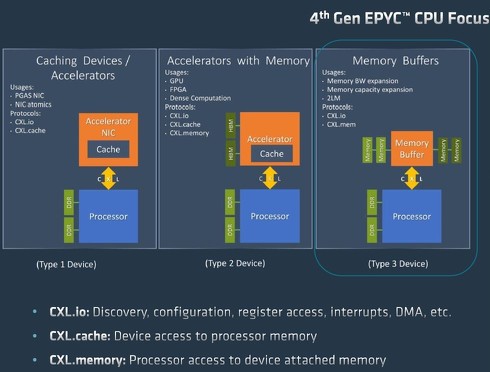

ここで少しだけ、CXL(Compute Express Link)について説明しよう。CXLには主に、2つの役割がある。1つは、GPU(グラフィックスプロセッシングユニット)やFPGA、NIC(ネットワークインタフェースカード)などのアクセラレーターとCPU(マイクロプロセッサ)を高速に接続するインタフェースとしての役割。もう1つは、メモリ領域を拡張するための高速メモリインタフェースとしての役割である。

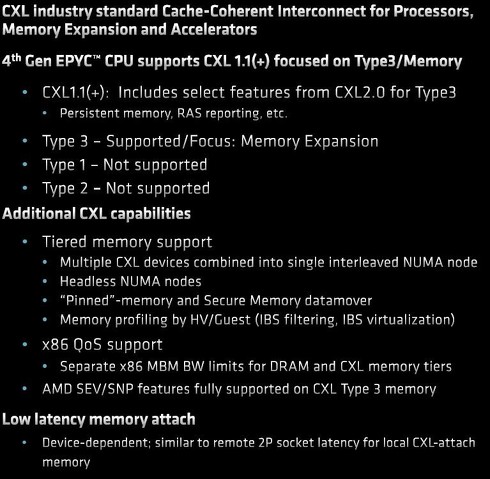

CXLは物理層としてPCIe Gen5を採用し、3種類の通信プロトコルを備える。通信プロトコルの組み合わせを変えた、「タイプ1」から「タイプ3」までの3種類のデバイス(CPUからCXLを通じて接続する半導体デバイス)がある。「タイプ1」のデバイスは、CPUのメモリにアクセス可能なアクセラレーター回路で、代表的なデバイスは「スマートNIC」だ。「タイプ2」のデバイスは、CPUのメモリにアクセス可能であり、なおかつ独自のメモリを備えるアクセラレーター回路である。代表的なデバイスはGPUやFPAなどだ。

そして「タイプ3」のデバイスは、「メモリバッファ」あるいは「メモリエキスパンダ」と呼ばれる、CPUとメモリやストレージなどの拡張記憶あるいは外部記憶をつなぐコントローラー回路である。第4世代EPYCがサポートするのは、このタイプ3だけだ。

128レーンのPCIe Gen5をベースとする入出力インタフェースの一部をCXLインタフェースとすることで、CXL対応のメモリバッファを介してDDR5タイプはもちろん、DDR4タイプやLPDDR4タイプなどのDRAMにも第4世代EPYCプロセッサがアクセス可能になる。メモリシステムの柔軟性が大幅に高まる。

CXL対応の順番が逆転したAMDサーバとIntelサーバ

なお、CXL対応メモリのサーバシステムを構築できるプロセッサは、AMDの「EPYC 9004シリーズ」が初めてとみられる。本来であれば最初にCXLをサポートするのはIntelのサーバ用次世代プロセッサ(開発コード名「Sapphire Rapids(サファイアラピッズ)」)のはずだった。当初の予定では2022年前半に製品がリリースされるはずであり、AMDの「EPYC 9004シリーズ」よりも早かった。

しかし実際には2回にわたって製品発表をIntelは延期した。11月9日にようやく、2023年(来年)1月に製品を正式に発表するとともに、HBM搭載品の製品名が「Xeon MAX」シリーズであることを明らかにした。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。 HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

米Western Digitalの「2023会計年度第1四半期」(2022年7月〜9月)を紹介する。 携帯型MP3プレーヤーの黎明期(1997年〜1998年)

携帯型MP3プレーヤーの黎明期(1997年〜1998年)

今回はフラッシュメモリを記憶媒体とする携帯型デジタルオーディオプレーヤー(DAP:Digital Audio Player)を扱う。時期は1997年〜1998年である。 ワイヤレス電力伝送で実際に電子機器を動作させる

ワイヤレス電力伝送で実際に電子機器を動作させる

今回は「7.4 試作例」の講演パートを解説する。ワイヤレス受電端末を試作し、低消費電力の小型機器をワイヤレス電力伝送で動かした。 ワイヤレス受電用端末の試作に向けたアンテナの設計作業

ワイヤレス受電用端末の試作に向けたアンテナの設計作業

今回は「7.2 アンテナ」と「7.3 アンテナの集積化」の内容について、簡単に解説する。 ワイヤレス電力伝送の過去から未来までを展望

ワイヤレス電力伝送の過去から未来までを展望

今回から、「IEDM 2021」でオランダimec Holst Centreでシニアリサーチャー、オランダEindhoven University of TechnologyでフルプロフェッサーをつとめるHubregt J. Visser氏が講演した「Practical Implementation of Wireless Power Transfer(ワイヤレス電力伝送の実用的な実装)」の内容を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める