RapidusとTenstorrent、2nmプロセスでのエッジAIアクセラレーター開発/製造で協業:NEDO採択プロジェクトの枠組みの中で

RapidusはTenstorrentと協業し、2nmプロセスベースのエッジAI(人工知能)アクセラレーターの開発/製造を行うと発表した。国際連携によって、生成AIを含むエッジ推論処理専用のエッジAIアクセラレーター開発を推進するという。

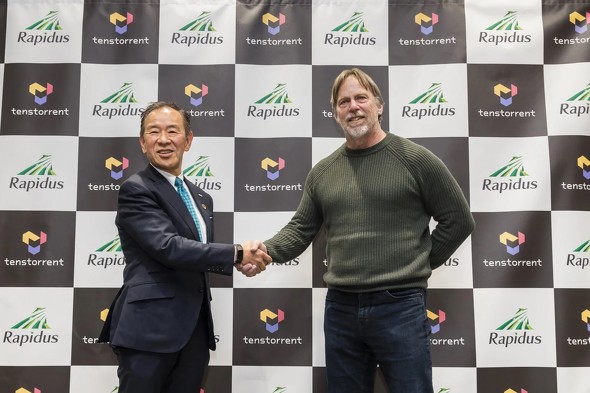

Rapidusは2024年2月27日、Tenstorrentと協業し、2nmプロセスベースのエッジAI(人工知能)アクセラレーターの開発/製造を行うと発表した。国際連携によって、生成AIを含むエッジ推論処理専用のエッジAIアクセラレーター開発を推進するという。

この協業は、経済産業省が「ポスト5G情報通信システム基盤強化研究開発事業」において技術研究組合最先端半導体技術センター(LSTC)を採択した研究テーマのうち、「2nm世代半導体技術によるエッジAIアクセラレーターの開発」の枠組みの中で行う。なお、経産省はこの研究テーマに280億円を支援する。

「Tenstorrentの設計技術ポテンシャルを最大限に引き出す」とRapidus

協業の中で、TenstorrentはCPUチップを開発し、アクセラレーターチップの開発は新エネルギー・産業技術総合開発機構(NEDO)が立ち上げた「AIチップ設計拠点」(AIDC)が担う。Rapidusは2nmプロセスベースの最先端ロジック半導体を製造する技術の有効性を引き出し、その製造を行うことを目指す。

Tenstorrentは2nmノードレベルのAIエッジデバイス開発で必要とされるRISC-V CPU設計技術および、チップレットIP(Intellectual Property)を有している。一方、Rapidusは設計支援/前工程/後工程を一貫して行うことで短TATでの半導体製造を実現する「Rapid and Unified Manufacturing Service(RUMS)」の構築を目指している。Rapidusは、「RUMSによる製品設計/製造は、Tenstorrentの設計技術ポテンシャルを最大限に引き出すために有効だ」と述べている。

2023年11月、RapidusとTenstorrentは2nmプロセスベースのAIエッジデバイス領域での半導体IPに関するパートナーシップ合意を発表していた。今回の協業はそのパートナーシップの事例となるという。

関連記事

RapidusがTenstorrentと提携、AIエッジ領域の開発を加速

RapidusがTenstorrentと提携、AIエッジ領域の開発を加速

Rapidusと、RISC-VプロセッサおよびAI(人工知能)チップを手掛けるTenstorrentが、2nmプロセスベースのAIエッジデバイス領域での半導体IPに関するパートナーシップに関して合意した。Tenstorrentは、「Rapidusとの技術提携を通じて、進化し続けるデジタル社会のニーズに応える最先端デバイスの開発を加速させる」としている。 Rapidusとも提携、Tenstorrentの現状と戦略

Rapidusとも提携、Tenstorrentの現状と戦略

2nmプロセスベースのAIエッジデバイス領域での半導体IPに関して、Rapidusと提携を結んだTenstorrent。同社CEOのJim Keller氏が今回、米国EE Timesのインタビューに応じ、事業の現状や戦略などを語った。 imecも全幅の信頼、Rapidusの「成功の定義」とは何か

imecも全幅の信頼、Rapidusの「成功の定義」とは何か

imecや経済産業省など、Rapidusの支援を公言する組織/企業は多い。さらに、米TenstorrentやフランスLetiなど、Rapidusとパートナーシップを締結する企業や機関も増えている。それはなぜなのか。2023年11月に開催された「ITF(imec Technology Forum) Japan」で見えてきたその理由と、Rapidusにとっての「成功の定義」をあらためて考えてみたい。 AIチップ設計拠点が23年4月に本格始動

AIチップ設計拠点が23年4月に本格始動

新エネルギー・産業技術総合開発機構は2023年3月17日、中小/ベンチャー企業などのAIチップ開発を加速するため、2019年から試験運転していた「AIチップ設計拠点」(東京都文京区)を2023年4月1日から本格運用すると発表した。 NTTら、400億円超の支援受け光電融合技術の開発加速へ

NTTら、400億円超の支援受け光電融合技術の開発加速へ

NTTは、新エネルギー・産業技術総合開発機構(NEDO)が公募した「ポスト5G情報通信システム基盤強化研究開発事業」の実施企業に採択された。研究に際し400億円超の支援を受ける予定で、光電融合技術の開発とIOWN(Innovative Optical and Wireless Network)事業の加速を目指す。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門