「電流を流すだけで積和演算」 TDKの超省電力AI用デバイス:消費電力はGPU比で100分の1(1/2 ページ)

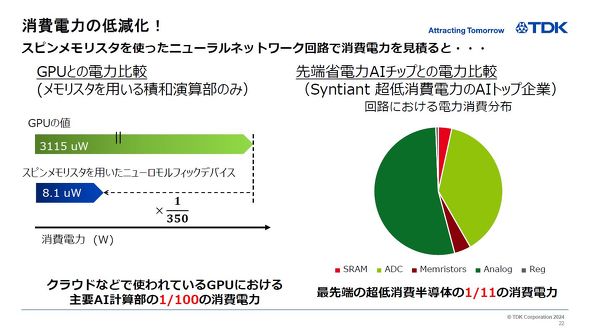

TDKは、スピントロニクス技術を活用するニューロモーフィック素子として「スピンメモリスタ」を開発した。AIで多用される積和演算を、GPUに比べて100分の1の消費電力で実行できるという。フランスCEAと東北大学との協業により、2030年の量産技術の確立を目指す。TDKは、スピンメモリスタのデモを「CEATEC 2024」で公開する予定だ。

TDKは2024年10月2日、スピントロニクス技術を用いたニューロモーフィック素子*)「スピンメモリスタ」を開発したと発表した。AI(人工知能)で使われれる積和演算を、GPUに比べて100分の1の消費電力で実行できるという。センサーと組み合わせて、センサーからのデータをローカルで処理するエッジAIでの活用が期待される。同年10月15日から開催される「CEATEC 2024」(幕張メッセ)で、スピンメモリスタを用いた音声分離のデモを披露する予定だ。

*)スピントロニクスは、電子が持つ電荷とスピンを活用する技術。ニューロモーフィック素子(デバイス)は、脳の神経細胞であるニューロンを模倣した回路で構成する演算器。

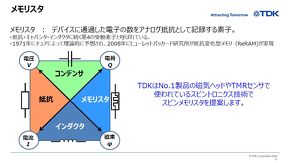

「第4の受動素子」メモリスタ

メモリスタは、デバイスを通過した電荷に応じて伝導度や抵抗値が変化する素子。抵抗、キャパシター、インダクターに続く“第4の受動素子”とも呼ばれている。TDKは、HDD用磁気ヘッドや磁気センサーなど向けに30年以上手掛けてきたスピントロニクス技術を応用し、2017年ごろにスピンメモリスタの開発に着手した。磁気抵抗効果も利用することで、安定したデータの保持や、制御のしやすさを実現したという。「これらの特徴は、メモリスタとして先行しているPCM(相変化メモリ)やReRAM(抵抗変化型メモリ)と大きく異なる点だ」(TDK)

AIの積和演算を超低消費電力で実行できるスピンメモリスタ

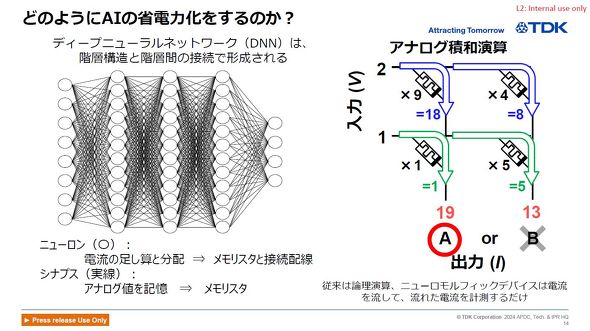

スピンメモリスタと電子回路で構成するニューロモーフィックデバイスは、AI推論で実行される膨大な積和演算を、超低消費電力で実行できる。

仕組みは次の通りだ。まずはスピンメモリスタをアレイ状に配列する。各メモリスタには、学習結果に応じて抵抗値が設定されている。推論を実行する際は、電流(推論のための入力情報に相当)をアナログまたはスパイクの状態でアレイに流し込む。電流はスピンメモリスタの抵抗値に応じて変化し、出力側へと流れていく。それらの出力電流を測定することで、入力情報の積和結果を得られる。

「AIに必要な計算を電流を流すだけで実現できるので、自然現象を活用した演算器ともいえる。積和演算を、GPUに比べて100倍以上効率的に実行できると期待されている」(TDK)

AIの普及に伴い、GPUやデータセンターの消費電力の増加が課題になっている。「GPUを使った演算ではプロセッサとメモリ間のデータのやりとりで電力を消費する。スピンメモリスタは、演算とデータ保存が同じ場所で行われるので、大幅に電力を削減できる」(TDK)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門