EE Times Japan >

LSI >

ミニダイ(チップレット)間接続におけるSTCO:福田昭のデバイス通信(509) TSMCが解説する最新のパッケージング技術(6)(2/2 ページ)

» 2026年03月05日 11時00分 公開

[福田昭,EE Times Japan]

ダイ間接続ピッチの短縮が帯域幅密度とエネルギー効率を高める

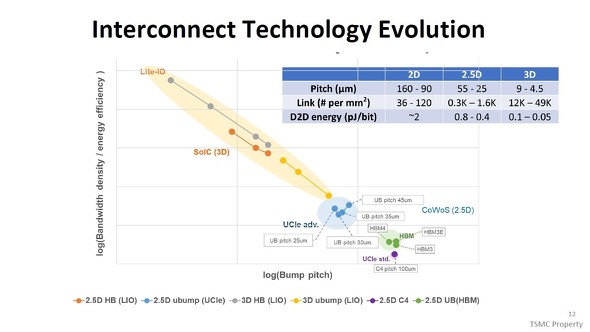

最初の項目である「(1)D2D and D2M bandwidth density/energy(ロジックのミニダイ間接続(D2D)とロジックとメモリの接続(D2M)における、消費エネルギー当たりの接続帯域幅密度)」では始めに、ミニダイ間を接続するバンプのピッチを狭くしていくと、帯域幅密度とエネルギー効率が大きく向上することを示した。

ミニダイ同士の接続手法には大別すると、複数のミニダイを基板上に横に並べて基板内配線を通じて相互に結線する手法(2Dあるいは2.5D)と、ミニダイを積層してダイレクトに接続、あるいはバンプを介して接続する手法(3D)がある。3D接続は接続ピッチを限界まで狭くできるので、帯域幅密度とエネルギー効率を最も高くすることが可能だ。

ミニダイ間を接続するバンプのピッチ(横軸、対数目盛り)と帯域幅密度およびエネルギー効率(縦軸、対数目盛り)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

ミニダイ間を接続するバンプのピッチ(横軸、対数目盛り)と帯域幅密度およびエネルギー効率(縦軸、対数目盛り)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)PPA(消費電力、性能、占有面積)を評価する

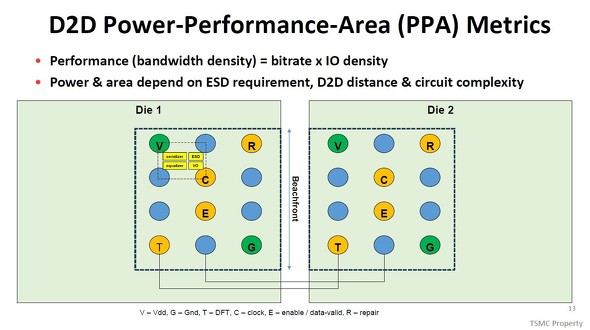

次に、2枚のミニダイ(チップレット)を中間基板(インターポーザ)に横に並べて相互に接続したときのPPA(消費電力、性能、占有面積)を評価する手法を述べた。性能すなわち帯域幅密度は、データ転送速度と信号入出力密度の積である。比較的単純だ。

ミニダイ間接続の消費電力と性能、占有面積(PPA:Power-Performance-Area)の評価指標。性能(帯域幅密度)はデータ転送速度と入出力ピン密度の積。消費電力と実装面積は静電気保護(ESD保護)要求仕様とミニダイ間距離、回路の複雑さによって変化する。図面はミニダイ間を接続するピン(端子)のレイアウト。「V」は電源端子、「G」は接地端子、「T」はテスト容易化設計(DFT)用端子、「C」はクロック入力端子、「E」はイネーブル/データ有効化端子、「R」はリペア用端子、そのほか(青色)は信号端子[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

ミニダイ間接続の消費電力と性能、占有面積(PPA:Power-Performance-Area)の評価指標。性能(帯域幅密度)はデータ転送速度と入出力ピン密度の積。消費電力と実装面積は静電気保護(ESD保護)要求仕様とミニダイ間距離、回路の複雑さによって変化する。図面はミニダイ間を接続するピン(端子)のレイアウト。「V」は電源端子、「G」は接地端子、「T」はテスト容易化設計(DFT)用端子、「C」はクロック入力端子、「E」はイネーブル/データ有効化端子、「R」はリペア用端子、そのほか(青色)は信号端子[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)消費電力と占有面積はやや複雑になる。チップレット接続では静電気保護(ESD保護)回路を搭載しなければならない。ESD保護の要求仕様が厳しいと、保護回路が複雑になり、消費電力が増加する。それからチップレット間の接続距離と、接続回路の規模が消費電力と占有面積に影響する。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

先進パッケージのシステム・製造協調最適化(STCO)

先進パッケージのシステム・製造協調最適化(STCO)

「IEDM 2025」におけるTSMCの講演内容を紹介する。今回は「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」を解説する。 インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化

前回に続き、「IEDM 2025」におけるTSMCの講演内容を紹介する。TSMCの2.5次元パッケージング技術「CoWoS(Chip on Wafer on Substrate)」において、インターポーザを低コスト化する技術を解説する。 複数のミニダイ(チップレット)を1つのパッケージに収容する

複数のミニダイ(チップレット)を1つのパッケージに収容する

2025年12月に開催された国際学会IEDMにおける、TSMCの講演を解説するシリーズ。今回は、前回に続き、「先進パッケージ技術の進化」を取り上げる。分割した複数のミニダイを同一パッケージに収容する際の、3つの接続手法を解説する。 AIサーバの高性能化に不可欠となった先進パッケージング技術

AIサーバの高性能化に不可欠となった先進パッケージング技術

2025年12月の国際学会IEDMで、TSMCが最新のパッケージング技術について講演した。本シリーズは、その内容の一部を紹介する。 メモリとストレージの動向を示す11個のキーワード(前編)

メモリとストレージの動向を示す11個のキーワード(前編)

2025年8月に開催された「FMS」の講演を紹介するシリーズ。今回はメモリとストレージの市場アナリストとして知られるJim Handy氏の講演を前後編でご紹介する。 2026年のHBM市況、カギを握るのは最新世代「HBM4」

2026年のHBM市況、カギを握るのは最新世代「HBM4」

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介するシリーズ。今回はTrendForceのアナリストであるEllie Wang氏の講演を取り上げる。広帯域メモリ(HBM)の生産能力や容量、価格を予測する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- データセンター用CPUでも勢力伸ばすRISC-V

Special SitePR

あなたにおすすめの記事PR