第9回 エミッタ接地回路のサプリメント 〜 エミッタ・フォロア 〜:Analog ABC(アナログ技術基礎講座)(2/3 ページ)

低入力インピーダンスが原因

図1(a)に示した増幅回路のどこに80Ω程度の入力インピーダンスがあるのでしょうか。ベースのバイアス抵抗(R1とR2の並列合成抵抗)は500Ωです。一見すると、80Ωの抵抗は回路図には見当たりません。実は、ベースのバイアス抵抗とベース自身の入力インピーダンスによって、80Ωの入力インピーダンスが形成されているのです。

トランジスタのエミッタには小さい抵抗(Rvt)があり*1)、26mAの電流を流した時には約1Ωになることを、これまでに何度か説明したことを思い出してください。ベースから見るとこの抵抗(すなわち、ベースの入力インピーダンス)は、電流増幅率β倍になります。エミッタ電流のおよそ1/βがベース電流ですから、抵抗としてはβ倍になるわけです。ここではβが100倍のトランジスタを使用していますので、ベースの入力インピーダンスは100Ωとなります。

エミッタ側にある20Ωの抵抗は、これと並列に挿入したコンデンサのインピーダンスがこの増幅回路を利用する周波数帯域では低くなっているので、影響を与えません。従って、2段目の入力インピーダンスは、ベースのバイアス抵抗500Ωとベース自身の入力インピーダンス100Ωの並列回路として考えることができるので、これらの合成抵抗を計算すると確かに80Ωとほぼ同じ83.33Ωとなります。

ここで、なぜベースのバイアス抵抗とベース自身の入力インピーダンスが並列なのか、と疑問に思うかもしれません。それは、扱う信号が交流の場合、電源(Vcc)側もグラウンド側も同じだと考えられるからです。R1は入力端子と電源端子の間に入っていますが、入力端子とグラウンドの間に入っているとも考えられるのです。つまり、電源端子に接続されているR1と、グラウンドに接続されているR2、エミッタとコンデンサを経由してグラウンドにつながっているベースの入力インピーダンスという3つすべてが並列に接続されています。

以上の83.33Ωを基に再度、減衰量を計算すると、シミュレーションで求めた−7dBとほぼ同じ−6.85dB(0.454倍)となります。せっかく増幅してもその半分が失われることになります。

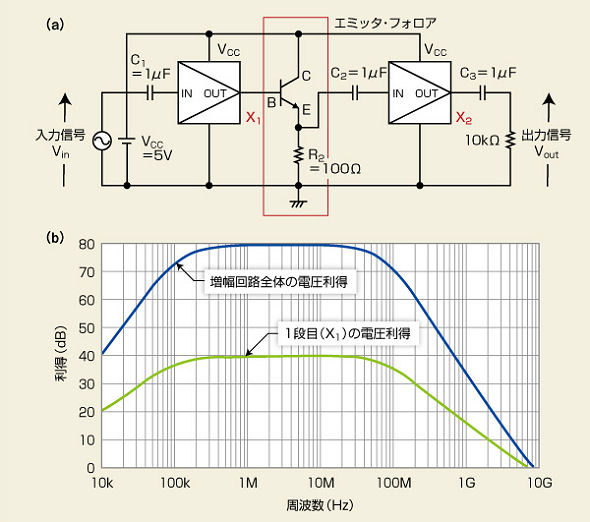

そこで、エミッタ・フォロアを追加して、この点を改善した例を、図3に示しました。図3(b)を見ると、1段目の出力信号が40dB近い利得で増幅され、増幅回路全体の利得も80dB近い値となっていることが分かります。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待