第30回 MOSFETのオペアンプを改善〜FET寸法の調整で入出力特性を向上〜:Analog ABC(アナログ技術基礎講座)(3/3 ページ)

グラウンド側での動作を分析

逆に、入力電圧がGNDに近づくと困ってしまうのが、電流源として動作するトランジスタX3です。

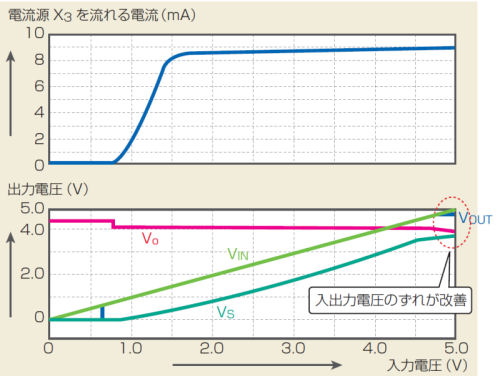

X7とX8で構成した差動対の両ゲートがGNDに近づけばソース電圧VsもGNDに接近します(図4下図の(2)の部分を参照してください)。VsがGNDに近づくということは、電流源X3のドレイン-ソース電圧Vdsが減少して流れる電流が減少することを意味しています(図4上図の(3)の部分を参照してください)。Vdsが小さくなると期待通りの電流が流れなくなります。

もし、VsがGNDまで下がってしまうと電流源X3の電流はゼロになってしまい、差動対の利得が無くなってしまいます。これまでに設計したオペアンプを使ったボルテージフォロアが、GNDまで動作しない理由は、入力段の電流源の電流が減少して、差動対が動作しなくなり、アンプの増幅能力が無くなるためといえます。

電源電圧付近において出力電圧が入力電圧に追従できないという電源側の問題は、トランジスタX8のVdsが減らないようにすれば、改善できそうです。

最も簡単な方法は、出力段のトランジスタX1のVgsを、X8のVgsより小さくしてしまうことです。たとえ、X8のゲート電圧がVddに達したとしても、X1のVgsがX8のVgsより小さければ、VoとVsはあたらずに済むからです。

今までのシミュレーションでは、全てのトランジスタのゲート長Lを0.18μm 、ゲート幅Wを20μmに設定していました。電源側の問題を解決するために、出力段トランジスタX1のみ、トラジスタのサイズを変更します。

Vgsを小さくするために、ゲート長Lを0.18μmのまま、ゲート幅Wを3倍の60μmに設定しました。改善後の図5を見ると、電源側の入出力電圧のずれが改善していることが分かります。

なんとかなるのがCMOSの面白さ

続いて、GND電圧付近において出力電圧が入力電圧に追従できないというGND側の問題を考えてみましょう。基本となる電流源が動作しなくなるので、こちらを直すのは簡単ではなさそうです。けれど、なんとかなってしまうのが、CMOS回路の面白さであり、エンジニア泣かせのところでもあります。

ところで、「MOS」の前に付くCの意味を覚えているでしょうか。これはComplimentaryの略で、相補的な回路が作れるということです。具体的に言うと、現在の回路はn型のMOSFETを使った差動対ですが、これにp型のMOSFETの差動対を追加することで、n型MOSFETが動作しない領域を補えます。回路図は以下の通り……といきたいところですが、具体的な回路の紹介は、次回に持ち越します。

Profile

美齊津摂夫(みさいず せつお)

1986年に大手の通信系ハードウエア開発会社に入社し、光通信向けモジュールの開発に携わる。2004年に、ディー・クルー・テクノロジーズに入社。現在は、同社の常務取締役CTO(最高技術責任者)兼プラットフォーム開発統括部長を務めている。「大学では電気工学科に所属していたのですが、学生のときにはアナログ回路の勉強を避けていました。ですから、トランジスタや電界効果トランジスタ(FET)を使ったアナログ回路の世界には、社会人になってから出会ったといっていいと思います。なぜかアナログ回路の魅力に取りつかれ、23年目になりました」。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増