「MEMSトランジスタ」をCMOSチップ上に作製、フィルタや発振器が集積可能に:プロセス技術 タイミングデバイス

CMOS技術で製造する半導体チップ上に、ギガヘルツオーダーの高周波信号源を集積し、タイミング生成機能を組み込めるという。研究チームによれば、これを応用することで、通信チャネル選択用フィルタや発振器などを、その他のCMOS回路とともに1枚のシリコンチップに搭載できるようになる。

米国の半導体研究コンソーシアム「Semiconductor Research Corporation(SRC)」とコーネル大学(Cornell University)は、「MEMS(Micro Electro Mechanical Systems)トランジスタ」を発表した。同コンソーシアムの参加企業は、CMOS技術で製造する半導体チップ上にタイミング生成機能を集積できるようになる。

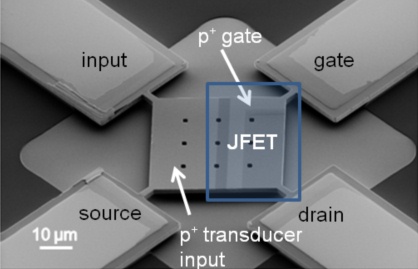

このMEMSトランジスタは、シリコン基板にCMOSプロセス技術で作り込んだ共振子の上に、接合型電界効果トランジスタ(JFET)を作製したもので、同コンソーシアムは「MEMS-JFET」と呼ぶ。共振子の機械的な振動によって生じる信号を増幅し、発振を生じさせて、正確なタイミング信号を生成する機能を果たす。これを使えば、通信チャネル選択用フィルタや発振器をCMOSチップ上に構成できるという。

SRCでデバイスサイエンス担当シニアディレクタを務めるKwok Ng氏は、「この研究成果によって、高周波の信号源も他のあらゆるCMOS回路と同様に、チップ上に直接集積できるようになるだろう」と述べている。

研究チームが今回開発した技術は、一般的なCMOSプロセスを使って、SOI(Silicon On Insulator)基板の上にMEMSとJFETを集積する。このMEMS素子は、単結晶シリコンの共振子である。酸化膜の犠牲層をエッチング処理で取り除くことで、空中にぶら下がった可動部を作り出す。JFETは、pn接合をトランスデューサとして利用することで、MEMS共振子の物理的な寸法で決まる固有周波数で発振する仕組みだ。

シリコン共振子の上にJFETを作製する。このJFETがトランスデューサとして機能し、信号を増幅して、発振を生じさせる役割を果たす。これを活用すれば、チャネル選択用フィルタや発振器をチップ上に作り込めるようになる。

シリコン共振子の上にJFETを作製する。このJFETがトランスデューサとして機能し、信号を増幅して、発振を生じさせる役割を果たす。これを活用すれば、チャネル選択用フィルタや発振器をチップ上に作り込めるようになる。このMEMS-JFETを使ったタイミング回路によって、発振器やフィルタを他の回路とともにCMOSチップ上に集積できるようになるため、現在のように水晶発振回路やCMOS/MEMSベースの発振器ICをボード上で外付けする必要は無くなるという。さらに研究チームは、今回の技術を用いれば、既存のMEMES共振器と比べて、共振の鋭さの指標であるQ値を高めるとともに効率を改善でき、ギガヘルツ(GHz)オーダーの周波数で動作できるようになると説明している。試作品は1.61GHzで動作し、Q値は室温で2万5900が得られているという。

研究チームによると、この技術で製造したタイミングデバイスはトランスデューサを別の材料で作製する必要が無いため、従来のMEMSよりも温度安定性に優れている。また、この技術では能動素子であるJFETを増幅器として利用するため、既存のMEMS発振器よりも位相雑音が低く、結果的にフリッカ雑音も低く抑えられると主張する。

なお今回の研究は、SRCの「Global Research Collaboration(GRC)」と「Focus Center Research Program Center for Materials, Structures and Devices」が資金を提供した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 全固体電池の製造プロセス簡素化、東北大が新手法

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める