1.4mm角、待機電流35μAのウェアラブル機器向けFPGA:プログラマブルロジック

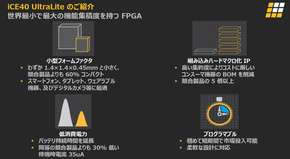

ラティスセミコンダクターは2015年2月、ウェアラブル機器など向けに低消費電力化、小型化を追求した新しいFPGA「iCE40 UltraLiteファミリ」を発表した。

ラティスセミコンダクターは2015年2月3日、ウェアラブル機器など向けに低消費電力化、小型化を追求した新しいFPGA「iCE40 UltraLiteファミリ」を発表した。最大1248LUTのユーザーロジック領域を持つFPGAで、待機電流35μA、パッケージサイズ1.4mm角を実現した。現在、エンジニアリングサンプルを出荷中で、2015年4月から量産を開始する。

累計2億5000万個を突破

同社は2012年から、主にモバイル機器向けに『最小のサイズ、最小の消費電力、最大の集積度』をコンセプトにFPGA「iCEファミリ」を展開。サムスン電子などのスマートフォンやタブレット端末などに採用され、2015年1月現在で累計2億5000万個以上を出荷したという。

最小のサイズ、消費電力

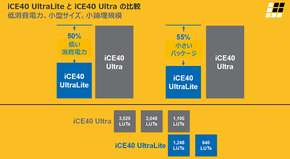

今回の発表したiCE40 UltraLiteは、iCEファミリの4つ目の製品ファミリで、最も消費電力、サイズを抑えた小型製品ファミリとして製品化した。iCE40 UltraLiteは、2014年発売の「iCE40 ULTRA」をベースに、スマートフォンよりも小型、低消費電力化が求められるウェアラブル端末などを意識し、機能を厳選することで小サイズ、低消費電力を実現した。そのため、採用する製造プロセスなどはiCE40 ULTRAと同じTSMC 40nmプロセスとなっている。

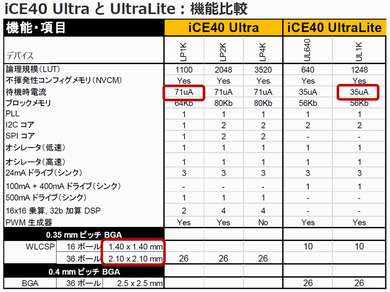

機能を絞ったものの「1000LUT程度の同じユーザーロジック領域を持つ競合FPGAと比較して豊富なハードウェアマクロIPを搭載している点がiCE40 UltraLiteの優位性の1つ」(同社)とする。具体的にはLED駆動などに使える3本の24mA定電流シンクや100mA+400mA定電流シンク、2系統のプログラマブルI2C、10KHzや48KHzのオシレータなどを内蔵する。またコンフィギュレーション用のSRAMやOTP(1回書き込み)メモリも備える。

豊富なハードウェアマクロIPを備えるものの「パッケージサイズは1.4×1.4×0.45mmで競合品よりも60%小さい。待機時消費電流も35μAで30%程度小さい」(同社)とする。

DSPの有無で選択できる

iCE40 UltraLiteは、1248LUT品と640LUT品の2種があり、それぞれ1.4mm角サイズの16ボールWLCSP(ボールピッチ:0.35mm)と2.5mm角サイズの36ボールBGA(ボールピッチ:0.4mm)の2つのパッケージが用意されている。

「従来のiCE40 ULTRAと、新製品のiCE40 UltraLiteの大きな違いはDSPの有無であり、信号処理が必要な場合はiCE40 ULTRA、信号処理の必要がなければiCE40 UltraLiteという選択になるだろう。スマートフォンなどでも、信号処理の必要がない用途は多数あり、幅広い用途にiCE40 UltraLiteを提案したい」(同社)としている。

なお、iCE40 UltraLiteの価格は、「大量受注時で50セントから」としている。

関連記事

モバイル機器向けのFPGA、2.1×1.7mmパッケージに乗算器や不揮発メモリを搭載

モバイル機器向けのFPGA、2.1×1.7mmパッケージに乗算器や不揮発メモリを搭載

モバイル機器向けのFPGAとして「iCE40」ファミリを展開しているラティスセミコンダクターは、同ファミリの新製品「iCE40 Ultra」を発表した。2.1×1.7mmのパッケージに、16ビット×16ビット乗算器や不揮発性コンフィギュレーションメモリ、I2CやSPIなどのハードマクロIPを搭載している。 「ウェアラブルは最も強みを生かせる分野」――ラティスCEO

「ウェアラブルは最も強みを生かせる分野」――ラティスCEO

ラティスセミコンダクター(Lattice Semiconductor)は、東京都内で記者説明会を開催し、ウェアラブル機器に向けた取り組みなどについて語った。シチズン時計の新型腕時計に同社のFPGAが採用されるなど、日本での事業にも弾みをつける。 サムスンのGALAXYも搭載! 低価格/小型FPGAで再浮上するラティスセミコン

サムスンのGALAXYも搭載! 低価格/小型FPGAで再浮上するラティスセミコン

ラティスセミコンダクターは、事業戦略説明会を開き、「われわれは、低消費電力、低コスト、小サイズのFPGAに注力する」(同社社長兼CEOを務めるDarin G.Billerbeck氏)との方針を示した。 20nmプロセスFPGAの量産始まる

20nmプロセスFPGAの量産始まる

ザイリンクスは2014年12月、20nmプロセスを使用したFPGA「Kintex UltraScale KU040」の量産を開始したと発表した。 Intel、Altera向けに14nmプロセスのFPGAを製造へ

Intel、Altera向けに14nmプロセスのFPGAを製造へ

Intelが、14nm FinFETプロセスを用いたFPGAを、Altera向けに製造すると発表した。アナリストは、「この契約によって、Intelはファウンドリメーカーとしての地位を確立することになるだろう」と分析している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増