TSMC、2015年半ばに16nm FinFETの量産開始へ:プロセス技術(1/2 ページ)

TSMCは、16nmプロセス以降のロードマップを明らかにした。まずは2015年半ばに、16nm FinFET+を適用したチップの量産を開始する。2016年には、10nmチップの生産工場の建設にも着手する。

TSMCは、コンパクト/低消費電力版の16nm FinFETプロセス技術を発表する予定であることを明らかにした。また、今後のプロセス技術の微細化についてもロードマップを発表している。2015年半ばには、16nm FinFET+(以降、16FF+)プロセス適用チップの量産を開始予定である他、2016年には、新たに10nmプロセス工場の建設にも着手する予定だという。

TSMCは、2014年に20nmプロセス適用チップの量産を開始してからわずか1年足らずで、16FF+の量産を発表したことになる。同社によると、16FF+プロセス適用チップは、競合製品に比べて10%高い性能を実現する他、20nmプロセスのSoC(System on Chip)と比べて消費電力量を半減し、サイクルタイムを2倍に拡大することが可能だという。

50製品以上をテープアウト

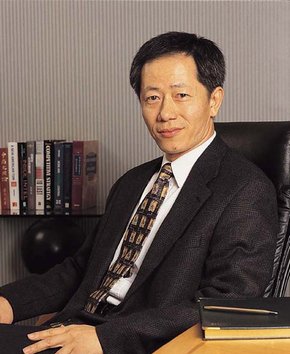

TSMCのプレジデント兼共同CEOであるMark Liu氏は、米国カリフォルニア州サンノゼで2015年4月7日に開催された「TSMC 2015 Technology Symposium」において、「2015年末までには、ファウンドリ工場において50製品以上をテープアウト(設計完了)できる予定だ。アプリケーションプロセッサやGPU、車載向けプロセッサ、ネットワークプロセッサなどに対応していきたい」と述べている。

Liu氏は、「当社は今、重大な岐路に立っている。各企業の成長をけん引しなければならない立場であると同時に、これまでにはない新しい企業としての形を追求していく必要がある。当社の消費者製品サイクルには特に変化はないが、製品設計や技術開発の進め方が大きく変化している。同じ期間内に達成すべき作業量が、増加の一途にあるためだ」と述べる。

ARMとの協業

さらに同氏は、「当社は、ARMとの協業により、CPUコア『Cortex-A72』を手掛けた。このCortex-A72は、16FF+を適用することで、『Cortex-A15』と比べて性能が3.5倍となり、消費電力が75%減となる見込みだ。TSMCとARMは引き続き、次世代プロセス技術開発において協業していく予定である」と付け加えた。

TSMCは、16nm FinFETプロセスのコンパクト版「16FFC」も開発している。ミッドレンジからローエンドのスマートフォンや、民生機器、ウェアラブル端末などに向けるという。16FFCの消費電力量は、従来の50%以上減となる0.55Vを実現。適用製品のテープアウトは2016年後半を見込んでいる。

米国の市場調査会社であるInternational Business Strategies(IBS)のCEOを務めるHandel Jones氏は、EE Timesの取材に応じ、「16FF/16FF+については、ゲート当たりのコストの上昇が見込まれるなど、コストに関する重大な課題が残る。しかし、16FFCではこうした課題が認識されていることから、特に低消費電力版を実現できれば、市場をけん引する存在となるだろう」と述べている。

TSMCは、Samsung Electronicsとの間で、16nm/14nm FinFETプロセス技術開発をめぐって競争を繰り広げている(TSMCの16nm世代は、他社でいえば14nm世代に相当するものだ)。Samsungは、「Mobile World Congress(MWC) 2015」(スペイン バルセロナ、2015年3月2〜5日)において、同社の最新スマートフォン「Galaxy S6」に14nm SoC「Exynos」を搭載すると発表した*)。TSMCの担当者は、競合他社に関するコメントを拒否しているが、今後、チップの生産量によって勝者が確定することになるだろう。

*)関連記事:Samsung「Galaxy S6 edge」を分解

Jones氏は、「Samsungは、既に14nm SoCのExynosの製造を開始したとしている。同社が、MWC 2015で発表を行った時点で量産を開始していたとしたら、TSMCの先を行っていることになる」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

TSMCのMark Liu氏 出典:TSMC

TSMCのMark Liu氏 出典:TSMC