ARMから見た7nm CMOS時代のCPU設計(9)〜CPUの性能向上に不可欠な設計の「手戻り」:福田昭のデバイス通信(20)(1/2 ページ)

今回は、LSI設計作業の所要時間について解説する。設計の各工程ではイタレーション、つまり「手戻り」と呼ばれる修正作業が発生する。CPUの動作周波数を上げるためには、膨大な数の手戻りが行われている。

LSI設計作業の所要時間

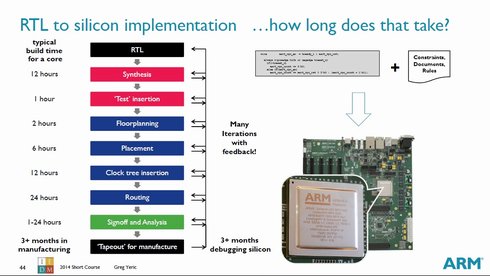

本シリーズの第3回では、LSIの設計作業における工程の流れを説明した。RTL(レジスタ転送レベル)記述から、シリコンマスクレイアウトまでの作業である。この作業には、どのくらいの時間がかかるのだろうか。

ARMの講演では、CPUコア設計作業の各工程における代表的な所要時間をスライドで説明していた。論理合成に12時間、テストパターンの作成に1時間、フロアプランに2時間、配置に6時間、クロックパターンの作成に12時間、配線に24時間、サインオフと解析に1時間〜24時間である。サインオフと解析を除いた所要時間は合計で57時間。2日半近くの時間がかかっている。サインオフと解析に24時間(1日)かかるとすると、3日半近くになる。

ただし実際には、設計の各工程で「手戻り(イタレーション)」と呼ばれる修正作業が発生する。講演では、この作業に3カ月程度の時間がかかるとしていた。膨大な数のイタレーションを繰り返していることが分かる。

イタレーションの繰り返しで動作周波数を上げる

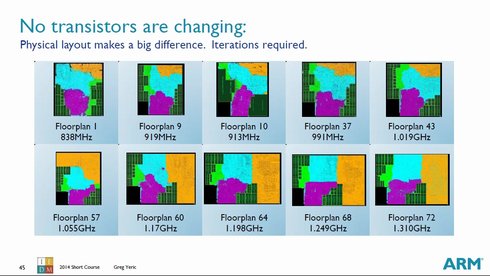

イタレーションを繰り返すのは、CPUの性能を上げるためである。設計不良を取り除く作業とは違う。性能を上げるためには、イタレーションは欠かせない。講演では、CPUの動作周波数を高めるために、マスクレイアウト(フロアプラン)をイタレーションによって変化させていったスライドを示していた。

このスライドによると、当初のフロアプラン(フロアプラン1番)による動作周波数は、838MHzだった。8回のイタレーションを経たフロアプラン9番では、動作周波数が919MHzに向上している。

ただし、イタレーションによって動作周波数が上がるとは限らない。下がることもある。つまり、失敗である。ARMが講演で示したスライドでは、フロアプラン9番では動作周波数が919MHzだったのが、修正したフロアプランであるフロアプラン10番では、動作周波数が913MHzに下がっている。

それでも全体としては、イタレーションの繰り返しによって動作周波数は上昇していく。フロアプラン43番で動作周波数が1GHzを超え、1.019GHzに達した。最後のフロアプラン72番では、動作周波数は1.310GHzに達している。当初の動作周波数が838MHzだったので、イタレーションの繰り返しによって動作周波数は1.56倍に向上したことになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険