EE Times Japan >

プロセス技術 >

ASMLがEUVリソグラフィ開発の最新状況を公表(4)〜次期主力機「NXE:3350B」の概要:SEMICON West 2015リポート(7)(2/2 ページ)

» 2015年09月01日 09時30分 公開

[福田昭,EE Times Japan]

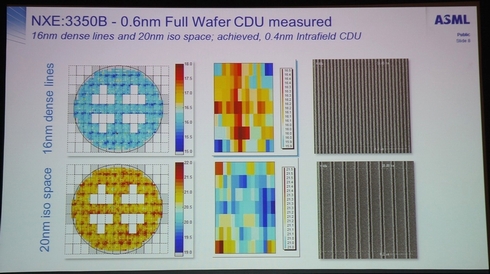

0.6nmと低い線幅ばらつきを16nm幅の直線パターンで得る

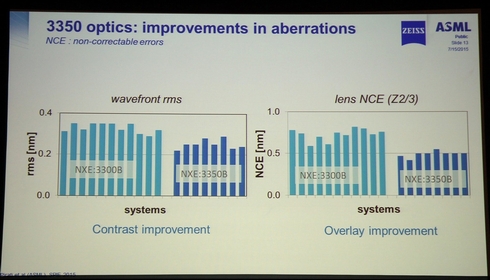

Lercel氏の講演では、「NXE:3350B」を評価した結果も示された。光学系ではレンズの波面収差とNCE(Non Correctable Error)がともに、NXE:3100に比べて減少した。言い換えると、光学系の解像力が向上した。

光学収差の比較。左は波面収差、右はNCE(Non Correctable Error)。いずれも現行主力機の「NXE:3300B」に比べ、次期主力機の「NXE:3350B」が減少している(クリックで拡大)

光学収差の比較。左は波面収差、右はNCE(Non Correctable Error)。いずれも現行主力機の「NXE:3300B」に比べ、次期主力機の「NXE:3350B」が減少している(クリックで拡大)実際、解像力の測定でも基本的な直線パターンとはいえ、かなり良好な結果を出している。ウエハー全面でのCDUは0.6nmと低い。露光領域でのCDUになるとさらに低く、0.4nmを得ている。16nm幅のち密な直線パターンと、20nm幅の孤立した直線パターンを露光した結果である。

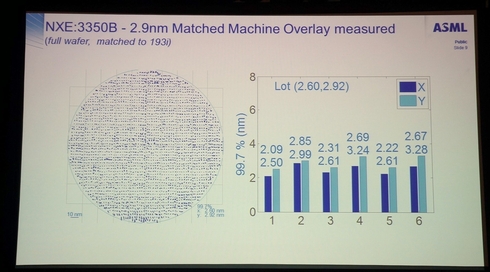

また装置間の重ね合わせ誤差(MMO)は、実験では2.9nmの誤差が出ていた。製品仕様には届かないものの、まだ改良の余地はある。

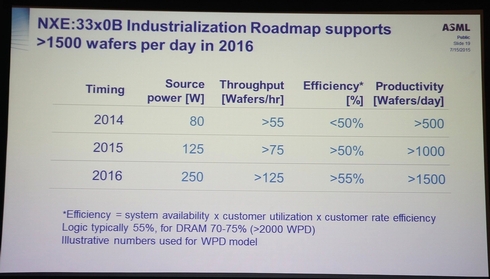

講演者のLercel氏はこの他、NXE:3300BやNXE:3350Bなどを含む「NXE:33x0」シリーズの開発ロードマップをスライドで見せていた。2014年は光源出力が80Wで生産性が500枚/日(24時間)であったのを、2016年には光源出力を250W、生産性を1500枚/日に向上させるという。かなり強気な目標である。

関連記事

次々世代のトランジスタを狙う非シリコン材料(1)〜なぜ非シリコンなのか

次々世代のトランジスタを狙う非シリコン材料(1)〜なぜ非シリコンなのか

今回からは、非シリコン材料を使ったMOSFET開発に焦点を当てる。微細化技術が行き詰まりを見せている中、非シリコンへの注目が高まっている。それはなぜなのか。また、非シリコン材料の候補には何があるのだろうか。 EUVは本当に実用化できるのか?

EUVは本当に実用化できるのか?

半導体製造技術のロードマップでは、193nmリソグラフィに限界が来たら、157nmフォトリソグラフィへと移行するはずだった。しかし、実際に普及したのは193nmの液浸リソグラフィであった。次の技術として名前が挙がるのはEUVだが、「この技術が実際に商業用途で利用されるかどうかは定かではない」と指摘する声がある。 「微細化は今後10年続く」――インテルの見解

「微細化は今後10年続く」――インテルの見解

米国で開催された「IEDM(International Electron Devices Meeting)2014」。Intelの14nm FinFETプロセスやTSMCの16nm FinFETなどの開発状況をはじめ、多くの論文が発表された。IEDM 2014のリポートを数回にわたってお届けする。 「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

「半導体微細化、技術的には7nmも可能」、TSMCの開発責任者がARMイベントで言及

半導体製造プロセスの微細化は、3次元構造を利用すれば7nmノードも不可能ではないという。だが、問題は技術ではなくコストにある。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR