EE Times Japan >

プロセス技術 >

着実に進歩するEUV、課題は光源:7nmプロセスでの実用化は可能なのか(2/2 ページ)

» 2016年01月28日 11時30分 公開

[Rick Merritt,EE Times]

DRAM工場のスループット向上にも期待

EUV装置は、ナノメートル単位で極めて高い精度を達成することができるという点において優れている。しかし、スループットや信頼性など、多くの面で後れを取っていることから、開口数を向上させて、5nmまたは3nmの線幅で使用できるようにする必要があるといえる。Van Hout氏は、「ASMLは現在、利害関係者との間で、EUV装置の構造やタイミングなどの詳細について話し合いを進め、性能向上の実現に向けた対策を講じているところだ」と述べている。

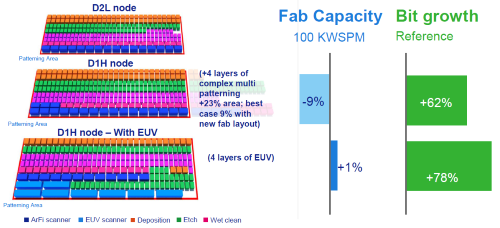

同氏は、EUV装置を使用しているDRAM工場の配置図を示しながら、「EUV技術は、工場のスループットを高め、プロセス工程を29〜32%削減することによって、生産量を7〜9%増加させることが可能だ」と主張する。既存の液浸装置で、16nm以降のプロセス技術で求められる微細なパターンを実現するには、ウエハーを何回も露光する必要がある。

ISSにおいて、IM Flash Technologiesの共同CEOであるGuy Blalock氏は、「われわれは、DRAMの製造におけるEUVリソグラフィについて、今後2〜3年以内に大きな決断を下すだろう」と述べた。同社は、IntelとMicron Technologyが2006年に設立したベンチャー企業である。

同氏は、「理論的には、EUV技術を使えば、生産性を15%向上できる。2018年には、EUVは、もはや無視できなくなるほどの技術になっているだろう」と語った。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 3D XPoint、開発から製造へ

3D XPoint、開発から製造へ

IntelとMicron Technologyが開発した「3D XPoint」は、製造の段階へと移る見込みだ。量産には12〜18カ月かかるとみられている。また、3D XPointでは、カルコゲナイド材料と「Ovonyx」スイッチが使われていることが明らかになった。 ASMLがEUV装置を15台受注、納品先はIntel?

ASMLがEUV装置を15台受注、納品先はIntel?

ASMLが、EUV(極端紫外線)リソグラフィ装置を15台、“米国顧客企業の1社”に納入すると発表し、業界の観測筋の間でさまざまな臆測を呼んでいる。複数の情報筋が、この顧客企業がIntelではないかという見方を示している。 TSMCが5nmプロセス開発に着手

TSMCが5nmプロセス開発に着手

TSMCが5nmプロセスの開発に着手する。ただし、EUV(極端紫外線)リソグラフィを採用するかどうかは、まだ不明だ。とはいえ、193nm ArF液浸リソグラフィを適用するには、かなりの数のパターニングが必要になり、コストが膨れ上がる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR

ASMLによれば、EUVリソグラフィを使えば、DRAM製造工場はスループットを向上できるとしている

ASMLによれば、EUVリソグラフィを使えば、DRAM製造工場はスループットを向上できるとしている