超高速DRAM技術「HBM」の基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(11)(2/2 ページ)

3D技術による超高速DRAM「HBM」

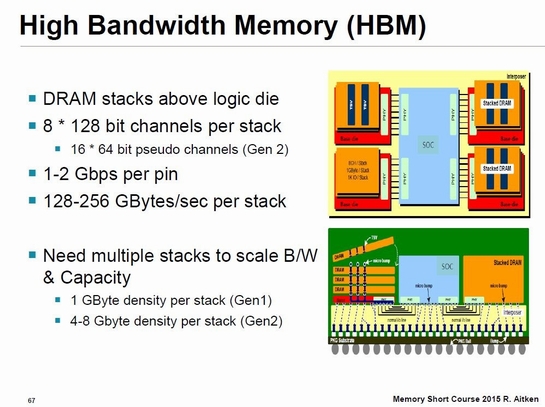

シリコンダイ積層技術とTSV技術によって実現した超高速DRAM技術の代表が、「HBM(High Bandwidth Memory)」である。最下層のロジックシリコンダイ(ベースチップ)と上層(2層、4層あるいは8層)のDRAMシリコンダイを積層したDRAMスタックで構成する。入出力数を1024ピンと極めて多くすることでピン当たりのデータ転送速度を抑えながら、全体の帯域幅(データ転送速度)を非常に大きく確保した。HBM全体の帯域幅(データ転送速度)は128Gバイト/秒(第1世代[詳しくは後述])あるいは256Gバイト/秒(第2世代)である。

HBMは単独のパッケージでは存在せず、ホストのプロセッサと組み合わせたマルチチップ・パッケージの形状で製品となる。ホスト側のCPUシリコンダイあるいはSoC(System on a Chip)シリコンダイとHBMスタックの間は、シリコンのインターポーザによって高密度に接続する。そして複数のHBMスタックとSoCをまとめて1つのパッケージに封止する。

HBMは第2世代から普及へ

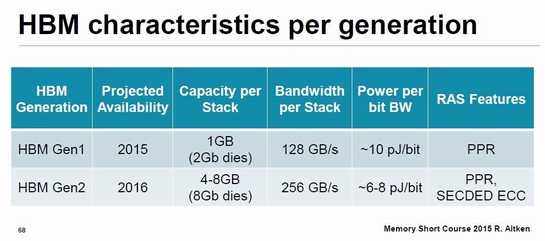

HBMの技術仕様は、業界団体のJEDECによって標準化が完了している。JEDEC標準の技術仕様には第1世代の「HBM Gen1(あるいはHBM1)」と第2世代の「HBM Gen2(あるいはHBM2)」が存在する。第1世代のHBMは2Gbit DRAMダイの積層を前提に技術仕様が策定されており、スタック当たりのDRAMダイ積層数は最多で4枚、記憶容量は最大で1Gバイト、帯域幅は最大で128Gバイト/秒とやや保守的な性能にとどまっていた。

これに対して第2世代のHBMは8Gbit DRAMダイを最多で8枚も積層することを想定した。かなりアグレッシブな性能を実現することを狙った技術仕様となっている。記憶容量は最大で8Gバイト、帯域幅は最大で256Gバイト/秒である。HBMは第2世代が本命の仕様といえる。

(次回に続く)

関連記事

超高密度のSRAM技術と超広帯域のDRAM技術

超高密度のSRAM技術と超広帯域のDRAM技術

セッション17とセッション18のテーマはメモリだ。セッション17では、Samsung Electronicsが、10nmのFinFETを用いた高密度SRAMの開発成果を披露する。メモリセルの面積が0.04μm2と、過去最小のSRAMセルを実現している。 ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。 シリコンの時代は「人類滅亡の日」まで続く(前編)

シリコンの時代は「人類滅亡の日」まで続く(前編)

私たちの日常に欠かせないものになっているシリコン半導体。シリコン半導体は、常に“文明の利器”の進化を支え続けてきたといっても過言ではないだろう。その地位は、今後も揺るがないはずだ。 DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

第1世代のHBM(HBM Gen1)と第2世代のHBM(HBM Gen2)の概要 出典:ARM

第1世代のHBM(HBM Gen1)と第2世代のHBM(HBM Gen2)の概要 出典:ARM