EE Times Japan >

FPGA >

Xilinx、エッジ〜クラウドの機械学習に対応:機械学習の推論能力、競合の6倍(2/2 ページ)

» 2017年03月14日 11時30分 公開

[馬本隆綱,EE Times Japan]

設計期間3週間を4日間に短縮した事例も

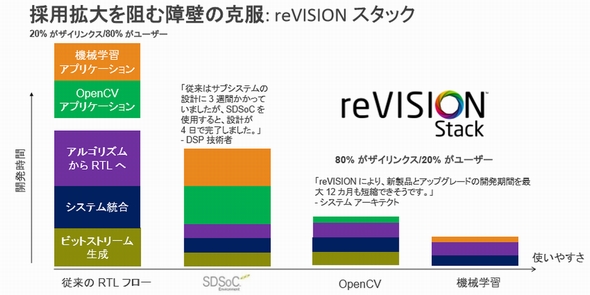

ザイリンクスによれば、機械学習に関連するサブシステムの設計に3週間を要していた。2年半前に発表した同社の開発環境「SDSoC」を用いると、この設計期間を4日に短縮したユーザー事例もある。reVISIONスタックを活用すれば、機械学習やOpenCVに関する開発負荷をさらに軽減することができるという。

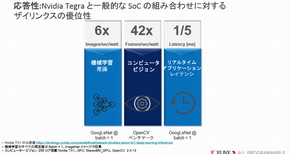

「ZynqSoC」や「MPSoC」を用いるreVISIONスタックは、応答性にも優れている。競合するGPUや標準SoCに比べて、機械学習の推論能力は1W、1秒当たりのイメージ数が最大6倍、コンピュータビジョン処理は1W、1秒当たりのフレーム数が42倍になるという。しかもレイテンシーは5分の1に抑えている。

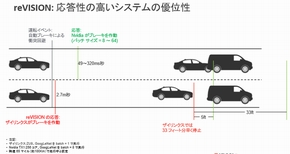

この応答性を自動車のブレーキシステムに適用した数値も明らかにした。「reVISIONスタックの場合、危険を察知して2.7ミリ秒後にブレーキが作動する。競合の他社製品では49〜320ミリ秒後に作動する。時速100kmで走行していると仮定すれば、競合製品を搭載した自動車に比べて1.5〜10mも手前に停車することができる」(Glaser氏)と、高速応答の重要性を強調した。

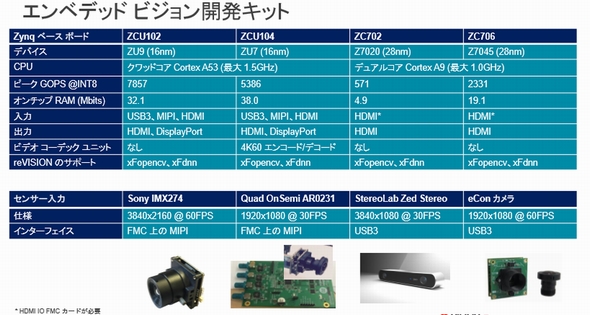

この他、ニューラルネットワークやセンサー領域での進化に対して、FPGAをベースとするSoC/MPSoCならではの柔軟な設計対応力も強みの1つとなっている。開発キットは搭載するデバイスによって、4種類を用意した。

なお、reVISIONスタックの供給は2017年第2四半期(4〜6月)より始める予定である。

関連記事

Xilinx、機械学習の推論に強いFPGAをアピール

Xilinx、機械学習の推論に強いFPGAをアピール

Xilinx(ザイリンクス)は2016年12月、データセンター向けのビジネスに関する記者説明会を都内で開催した。 FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手ベンダーで唯一買収されずに生き残っているXilinx。同社日本法人のザイリンクス社長で韓国のVice Presidentを務めるSam Rogan(サム・ローガン)氏に国内の戦略を聞いた。 IIoTを実現するプラグラマブルSoC、Xilinx語る

IIoTを実現するプラグラマブルSoC、Xilinx語る

Xilinxの日本法人(ザイリンクス)は、2016年10月4〜7日に幕張メッセで開催された「CEATEC JAPAN 2016」の講演で、インダストリアルIoT(IIoT)を実現する取り組みについて語った。 16nm MPSoCにRFデータコンバーターを統合

16nm MPSoCにRFデータコンバーターを統合

Xilinx(ザイリンクス)は、RFクラスのアナログ技術を統合した「All Programmable RFSoC」について、その技術概要を発表した。 自動運転でFPGAの期待値高まる、ザイリンクスがデモ

自動運転でFPGAの期待値高まる、ザイリンクスがデモ

ザイリンクスは、「第9回 国際カーエレクトロニクス技術展」(2017年1月18〜20日、東京ビッグサイト)で、ディープラーニングを使った歩行者認識、IRカメラによるドライバーモニタリングシステム、Ethernet AVBを使った高速伝送のカメラシステムなど、ADAS(先進運転支援システム)や自動運転向け技術をデモ展示した。 2.5Dパッケージング技術を適用したFPGA

2.5Dパッケージング技術を適用したFPGA

現在、米国で行われている国際学会「ISSCC 2017」で、Intelが、2.5Dパッケージング技術を使ったFPGAについて論文を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR