Intelの高性能・高密度パッケージング技術「EMIB」の概要:福田昭のデバイス通信(109) TSMCが解説する最先端パッケージング技術(8)

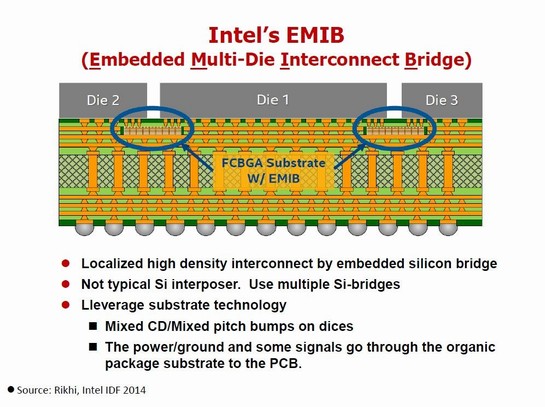

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。

Intelの大規模FPGA製品にEMIB技術を採用

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンドリー最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、CoWoS(Chip on Wafer on Substrate)技術を含めた、シリコンインターポーザ技術のパッケージを製品化した事例をご報告した。今回は、Intelが開発した、2.nD(2.n次元)の高性能・高密度パッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」の概要を説明する。

EMIBは、小さなシリコン基板に形成した微細な高密度配線を介することで、隣接するシリコンダイを近接搭載するパッケージング技術で、Intelが2015年12月に買収を完了したAlteraの、ハイエンドFPGA「Stratix 10 SoC」シリーズに採用した(現在の製品ブランドは「Intel FPGA」)。またIntelは、シリコンファウンドリー事業の一環として、EMIB技術によるパッケージング・サービスを提供している。

小さなシリコン基板によって隣接するシリコンダイを近接して搭載

EMIB技術では、シリコンインターポーザを使わない。その代わりに、「シリコンブリッジ(silicon bridge)」と呼ぶ、小さなシリコン基板をパッケージの樹脂基板に埋め込む。シリコンブリッジの表面に微細かつ高密度な配線を形成することで、隣り合うシリコンダイをギリギリまで近づけてパッケージ基板に搭載できるようにする。

シリコンブリッジを使うことの利点は、シリコンインターポーザ技術に比べると追加するシリコンの面積が小さくて済むことだ。これは追加コストの抑制につながる。またシリコンダイの数が増えたときでも、シリコンブリッジの数を増やして対応するので、コストがあまり増加しない。シリコンインターポーザ技術ではシリコンダイの数が増えると、インターポーザのシリコン面積が巨大になり、コストが急激に増加するという弱点がある。

シリコンブリッジはまた、シリコン貫通ビア(TSV: Through Silicon Via)を形成しない。このことも、TSVを使うシリコンインターポーザに比べ、追加コストの削減につながる。

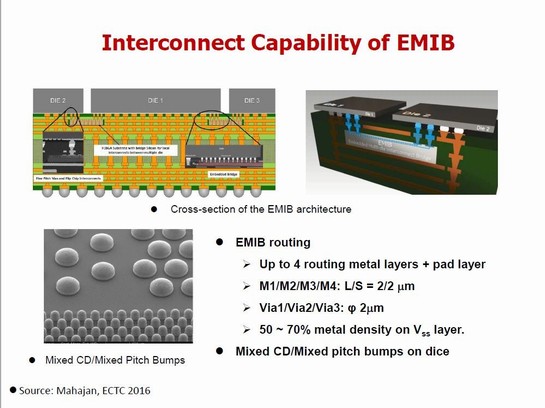

シリコンブリッジに微細かつ高密度な4層配線を形成

国際学会でIntelが発表したEMIB技術によると、シリコンブリッジには4層の配線と1層のパッドを形成する。配線の幅と間隔は2μmと細い。配線間を接続するビアの直径は2μmとこれも小さい。

シリコンブリッジにはシリコンダイの種類に応じて、さまざまな大きさのパッドとバンプを形成する。バンプの大きさ(直径)は50μm〜100μm程度とみられる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

高性能コンピューティング向けの2.nD(2.n次元)パッケージング技術

高性能コンピューティング向けの2.nD(2.n次元)パッケージング技術

2012年ごろから、主に高性能コンピューティング(HPC)分野では「CoWoS(Chip on Wafer on Substrate)」の製品化が進んだ。その最大の特長であるシリコンインターポーザは優れた技術なのだが、コストが高いのが難点だった。そのため、CoWosの低コスト版ともいえる2.nD(2.n次元)のパッケージング技術の提案が相次いだ。 TSMCの1強時代に幕? “2ファブ・オペレーション”が可能になった14/16nm世代

TSMCの1強時代に幕? “2ファブ・オペレーション”が可能になった14/16nm世代

今回は昨今、発表が相次いでいる新しいGPUのチップ解剖から見えてくる微細プロセス、製造工場(ファブ)の事情を紹介する。チップ解剖したのはNVIDIAの新世代GPUアーキテクチャ「Pascal」ベースのGPUと、ゲーム機「PlayStation 4 Pro」にも搭載されているAMDのGPUだ。 インテル、FPGA戦略の踏襲をコミット

インテル、FPGA戦略の踏襲をコミット

Intel(インテル)のグループ会社である日本アルテラは、東京都内で「インテルSoC FPGAデベロッパー・フォーラム(ISDF)」を開催した。SoC FPGAの製品戦略などについて、これまでの方向性を踏襲していくことを表明するとともに、会場では“インテル色”を全面に打ち出した。 Intel、Altera製品のサポート加速を明言

Intel、Altera製品のサポート加速を明言

Intelは、米国で開催した「Intel SoC FPGA Developer Forum(ISDF) 2016」において、Altera製品のサポートを強化すると強調した。 太陽誘電とGEが電子部品内蔵技術で協業

太陽誘電とGEが電子部品内蔵技術で協業

太陽誘電とGEベンチャーズの両社は2016年7月、2014年末から半導体パッケージ基板などに応用可能なワイヤボンド不要の電子部品内蔵基板技術分野で協業していることを明らかにした。 Samsungの売上高がIntelを超える可能性も

Samsungの売上高がIntelを超える可能性も

DRAMとNANDフラッシュメモリの価格が上昇していることから、2017年第2四半期(4〜6月期)におけるSamsung Electronicsの売上高が、Intelを超える可能性が出てきた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」