究極の高密度不揮発性メモリを狙う強誘電体トランジスタ:福田昭のストレージ通信(73) 強誘電体メモリの再発見(17)(1/2 ページ)

今回は、1個のトランジスタだけでメモリセルを構成できる「FeFET(Ferroelectric FET)」または「強誘電体トランジスタ」について解説する。FeFETは、構造はシンプルだが、トランジスタの設計はかなり複雑になる。

» 2017年09月05日 10時30分 公開

[福田昭,EE Times Japan]

強誘電体を電界効果トランジスタのゲート絶縁膜に導入する

本シリーズの第17回(前々回)では、強誘電体を使ったメモリセルの構造について簡単に説明した。1つはDRAMと似た構造のセルで、1個のトランジスタと1個の強誘電体キャパシターで構成する。トランジスタがセル選択素子、強誘電体キャパシターが記憶素子、という役割り分担になる。

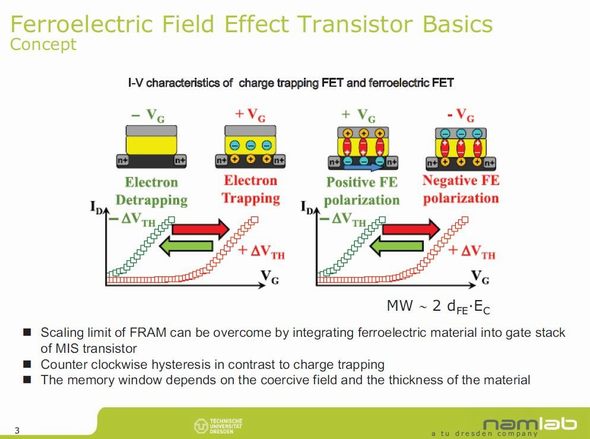

もう1つは電荷捕獲(チャージトラップ)方式フラッシュメモリと似た構造のセルで、MOSトランジスタ(MOSFET)のゲート絶縁膜を強誘電体にすることで、1個のトランジスタだけでメモリセルを構成する。強誘電体ゲート絶縁膜のトランジスタ(FET)が、セル選択素子と記憶素子の両方を兼ねる。このようなトランジスタを「FeFET(Ferroelectric FET)」「強誘電体トランジスタ」などと呼んでいる。1個のトランジスタだけでメモリセルを構成できるので、究極ともいえる、高密度なメモリを原理的には実現可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- キオクシアが超高IOPS SSD開発 NVIDIA Storage-Nextに対応

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

Special SitePR

あなたにおすすめの記事PR