日立、CMOSアニーリングマシンを名刺形状で実現:エネルギー効率は従来の約17万倍

日立製作所は、従来型コンピュータに比べて処理性能を約2万倍、エネルギー効率を約17万倍に高めた名刺サイズのCMOSアニーリングマシンを開発した。

スマホなどで組み合わせ最適化問題の計算が可能に

日立製作所は2019年2月、従来型コンピュータに比べて処理性能を約2万倍、エネルギー効率を約17万倍に高めた名刺サイズのCMOSアニーリングマシンを開発したと発表した。集積度を高める回路技術とチップ間接続技術を新たに開発することで実現した。

CMOSアニーリングマシンは、イジングモデルを用いて組み合せ最適化問題を解くために開発している新型コンピュータ。同社はこれまで、FPGAを用いたCMOSアニーリングチップを25個接続して、10万2400パラメーターの問題に対応できるCMOSアニーリングマシンを開発してきた。パートナー向けにクライドサービスも2018年8月より提供している。

今回は、CMOSアニーリングマシンをスマートフォンやカメラ、センサーなどのIoT(モノのインターネット)機器に実装し、エッジ側で組み合わせ最適化問題の計算をリアルタイムに処理する用途を視野に入れて開発した。

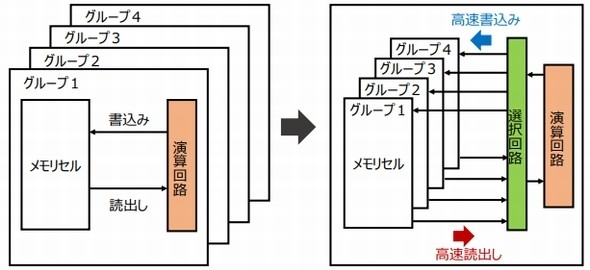

これを可能にするため、日立は大きく2つの技術を開発した。その1つが「高集積化を実現するための回路技術」である。CMOSアニーリングマシンの最適化問題を計算するためにこれまで、パラメーターを4グループに分け、グループごとに順次計算していた。このため、パラメーターグループの数だけ演算回路を用意する必要があった。

今回、パラメーター値を保持するメモリセルに対して、高速にアクセスする技術を開発した。これにより、1つの演算回路で演算順序に従い、4つのパラメーターグループを切り替えながら共有することが可能となった。演算回路数を削減できることで、メモリセルの集積度は従来の1.5倍となり、1チップで3万976のパラメーターを集積することに成功した。

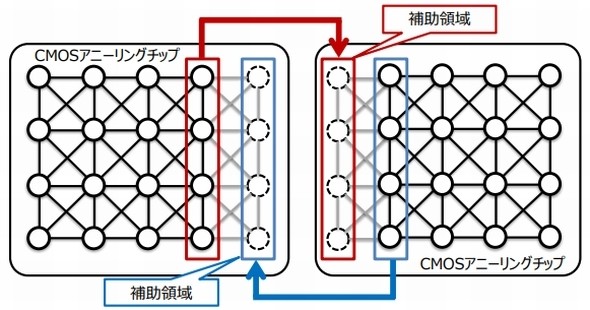

もう1つは「高速計算を可能にするチップ間接続技術」である。最適化問題の計算は、個々のパラメーター値と、それに隣接するパラメーター値を用いて計算する。このため、半導体チップ間でパラメーター値を転送する必要がある。従来はこの時に遅延が生じていた。

これを解決するため、新たなチップ間接続技術を開発した。半導体チップの端部に、別チップのパラメーター値をコピーするための補助領域を設けた。これにより、あるパラメーターグループを計算している間に、次のパラメーターグループをコピーしておくことができるという。

これらの技術を適用して開発したチップ2個を接続し、外形寸法が91×55mmのCMOSアニーリングマシンを開発した。ランダムに生成したイジングモデルのアニーリング計算を実行し、その性能を検証した。約6万パラメーターの組み合わせ最適化問題の計算を行ったところ、従来型コンピュータに比べて処理性能は約2万倍、エネルギー効率は約17万倍となった。

なお研究成果の一部を、半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference) 2019」(2019年2月17〜21日、米国カリフォルニア州サンフランシスコ)で発表した。

関連記事

車載制御マイコン、ハードによる仮想化が可能に

車載制御マイコン、ハードによる仮想化が可能に

ルネサス エレクトロニクスは、次世代の車載制御マイコンに向けて、ハードウェアによる仮想化支援機構や、スタンバイ‐レジューム自己故障診断(SR‐BIST)機能などを開発した。フラッシュメモリ混載28nm低電力プロセスを用いてテストチップを試作し、これらの機能について動作を確認した。 東工大、極低消費電力のデジタルPLLを開発

東工大、極低消費電力のデジタルPLLを開発

東京工業大学は、消費電力が極めて小さい分数分周タイプのデジタル位相同期回路(PLL)を開発した。従来の開発品に比べて消費電力を60%削減できるという。 広島大学ら、300GHz帯トランシーバーICを開発

広島大学ら、300GHz帯トランシーバーICを開発

広島大学、情報通信研究機構(NICT)、パナソニックは、シリコンCMOS回路を用いた300GHz帯ワンチップトランシーバーICを共同開発した。80Gビット/秒のデータ伝送が可能となる。 ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

2019年2月17〜21日に米国カリフォルニア州サンフランシスコで開催される半導体回路技術関連の国際学会「ISSCC 2019」は、発表内容のほとんどが、機械学習(マシンラーニング)や高速ネットワーク、メモリが主役となる“データ時代”に関するものとなりそうだ。 日立、演算規模が可変なCMOSアニーリングマシンを開発

日立、演算規模が可変なCMOSアニーリングマシンを開発

日立製作所は2018年6月15日、解くべき問題に対応して演算規模をスケーラブルに構成できる世界最大規模のCMOSアニーリングマシンを開発し、同年8月よりパートナー向けにクラウドサービスとして公開すると発表した。 日立、新構造のSiCパワーデバイス「TED-MOS」を発表

日立、新構造のSiCパワーデバイス「TED-MOS」を発表

日立製作所は、新構造を採用することで耐久性を高めたSiC(炭化ケイ素)パワー半導体「TED-MOS」を開発した。50%の省エネが可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

高集積化に向けた回路技術の概略 出典:日立

高集積化に向けた回路技術の概略 出典:日立 チップ間接続の概略 出典:日立

チップ間接続の概略 出典:日立 開発したCMOSアニーリングマシンの外観 出典:日立

開発したCMOSアニーリングマシンの外観 出典:日立