クロスポイント化に期待がかかる抵抗変化メモリ(ReRAM):福田昭のストレージ通信(151) 半導体メモリの技術動向を総ざらい(12)(2/2 ページ)

» 2019年06月19日 11時30分 公開

[福田昭,EE Times Japan]

抵抗変化メモリ(ReRAM)の長所と将来性

ReRAMは当初、1個のセル選択トランジスタと1個の記憶素子でメモリセル(1T1Rセル)を構成し、そのメモリセルをアレイ状に配列する方式で研究開発が進められた。ごくふつうの方式である。

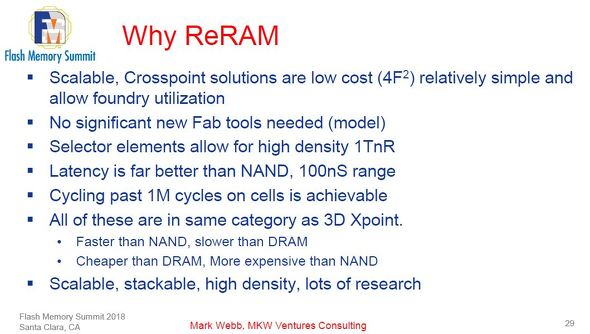

この方式で開発されたReRAMの読み出し遅延時間は100ナノ秒、書き換えサイクル寿命は100万回と、いずれもNANDフラッシュメモリよりも良好な値を得ている。ただし記憶密度はあまり高くない。NANDフラッシュメモリはもちろんのこと、DRAMにも及ばない。

そこで記憶密度向上の手段として期待がかけられているのが、クロスポイント化である。原理的には3次元積層のクロスポイント構造により、記憶密度をDRAMよりも高くできる。ただし、NANDフラッシュメモリに比べると記憶密度は低い。

クロスポイント構造のReRAMは過去に、パナソニックが2層構造で記憶容量が8Mビットのシリコンダイ、東芝とSanDisk(現在はWestern Digital)の共同研究グループが2層構造で記憶容量が32Gbitのシリコンダイをそれぞれ、国際学会で発表している。パナソニックの発表は2012年のISSCC、東芝とSanDiskの共同発表は2013年のISSCCである。またソニーが、100Gビット級のReRAMをクロスポイント構造によって開発中だとされる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

磁気抵抗メモリ(MRAM)の技術動向と製品動向

磁気抵抗メモリ(MRAM)の技術動向と製品動向

今回は、MRAMの技術開発状況と製品化動向を取り上げる。特に、最近のMRAM開発で注目されている埋め込みメモリについて解説する。 磁気抵抗メモリ(MRAM)の長所と短所

磁気抵抗メモリ(MRAM)の長所と短所

今回から磁気抵抗メモリ(MRAM)について解説する。まずはMRAMの構造と、長所、短所をそれぞれ説明しよう。 「3D XPointメモリ」開発のオープン・モードとステルス・モード

「3D XPointメモリ」開発のオープン・モードとステルス・モード

今回は、「3D XPointメモリ」の研究開発が、オープン・モードで始まり、後半はステルス・モードとなっていたことを説明する。 メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動

メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動

世界半導体市場統計(WSTS)のデータを用いて市場動向をグラフにしてみたところ、両者の挙動が大きく異なることを発見した。本稿では、その挙動を示すとともに、その理由を考察する。その上で、二つのメモリ市場の未来を展望する。 Micron広島工場の新棟が完成、1Y/1Znm生産加速

Micron広島工場の新棟が完成、1Y/1Znm生産加速

Micron Technology(以下、Micron)は2019年6月11日、同社広島工場の新製造棟(B2棟)の完成と生産開始を記念し、オープニングセレモニーを行った。新棟では、10nm台の第2世代となる「1Ynm」プロセスでの生産を開始。2019年末には、同第3世代である「1Znm」の生産も開始する計画だ。 64層3D NANDを用いた256GBの車載用eMMC、WDが発表

64層3D NANDを用いた256GBの車載用eMMC、WDが発表

Western Digital(ウエスタンデジタル)は2019年5月30日、車載向けとして、TLC(Triple Level Cell)タイプの64層3D NANDフラッシュメモリを搭載したeMMCの新製品「Western Digital iNAND AT EM132 EFD(以下、iNAND AT EM132)」を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR