実装工程の生産性をマウンタの速度が大きく左右:福田昭のデバイス通信(266) 2019年度版実装技術ロードマップ(74)(1/2 ページ)

今回は実装工程の生産性を左右する2つの要因を解説する。1つは実装設備(主にマウンタ)の速度、もう1つはマウンタにおける部品の補充や段取り換えなどに要する時間である。

実装工程の生産性を左右する2つの要因

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第74回である。

本シリーズの第3回から第22回までは第2章「注目される市場と電子機器群」の概要、第23回から第30回までは第3章「電子デバイスパッケージ」の概要、第31回から第63回までは第4章「電子部品」の概要、第64回から第72回までは第5章「プリント配線板」の概要を説明してきた。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。前回(第73回)から、第6章「実装設備」(プログラムの10番)の概要を紹介している。出典:JEITA(クリックで拡大)

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。前回(第73回)から、第6章「実装設備」(プログラムの10番)の概要を紹介している。出典:JEITA(クリックで拡大)前回(第73回)からは、第6章「実装設備」の内容を報告している。今回は第6章第2節の「生産性の動向」から、概要をご説明する。実装工程の生産性を大きく左右する要因は主に2つ。1つは実装設備(主にマウンタ)の速度、もう1つはマウンタにおける部品の補充や段取り換えなどに要する時間である。

マウンタの技術ロードマップ(2018年〜2028年)

「マウンタ(部品搭載機)」は、大きさと形状の異なる多種多様で数多くの部品(表面実装部品)をプリント配線板に搭載する。部品の搭載が始まってから完了するまでの期間、プリント配線板はマウンタの内部にとどまる。この時間をなるべく短くすることが、生産性の向上につながる。

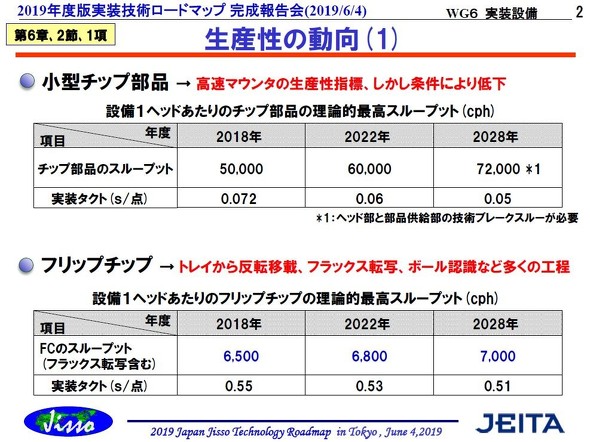

マウンタの性能(速度)は、1時間当たりに何個の部品(チップ)を搭載できるか(スループット(cph:chip per hour))、あるいは1個の部品を搭載するのに何秒が必要か(実装タクト(秒/点))で表記される。いずれも1個の搭載ヘッド当たりの性能である。

チップ抵抗やチップコンデンサーなどを対象とするマウンタ(チップマウンタ)のスループットは現在、理論的な最高値で5万cpsに達する。実装タクトでは0.072秒/点であり、極めて短い時間で1個のチップ部品を搭載していることが分かる。

マウンタでも半導体のベアチップを対象とするフリップチップボンダになると、理論的な最高値はかなり低下する。それでもスループットで6500cps、実装タクトで0.55秒/点という性能が得られている。なお搭載精度は±7μm前後を想定した。

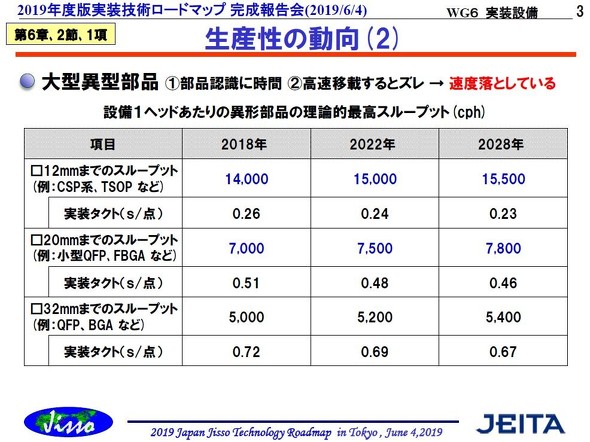

また、さまざまな形状の半導体パッケージや非チップの受動部品などを対象とする異型部品マウンタでは、半導体パッケージの大きさによってスループットが大きく変化する。外形寸法が12mm角以下の小さな半導体パッケージ(CSPやTSOPなど)では、理論的な最大スループットは1万4000cphとかなり高い。

しかし外形寸法が20mm角以下の半導体パッケージ(QFPやFBGAなど)になると、理論的な最大スループットは半分の7000cpsに低下する。外形寸法が32mm角以下とさらに大きくなると、理論的な最大スループットは5000cpsに下がる。また異型部品マウンタには一般的なノズルによる吸着が困難で専用チャックで部品を把持するタイプや、圧入方式のコネクター(プレスフィットコネクター)に対応したタイプが用意されており、これらの部品が存在するとスループットは著しく低下する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長