SiC-MOSFETの電子移動度が倍増、20年ぶりに大幅向上:京大が再び快挙(2/2 ページ)

» 2020年09月09日 09時30分 公開

[村尾麻悠子,EE Times Japan]

SiC-MOSFETの電子移動度が2倍に

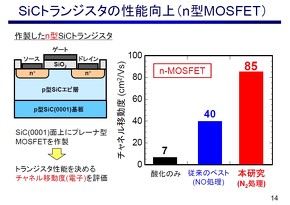

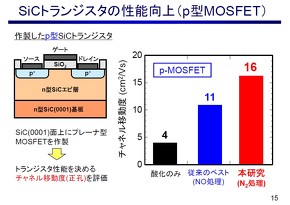

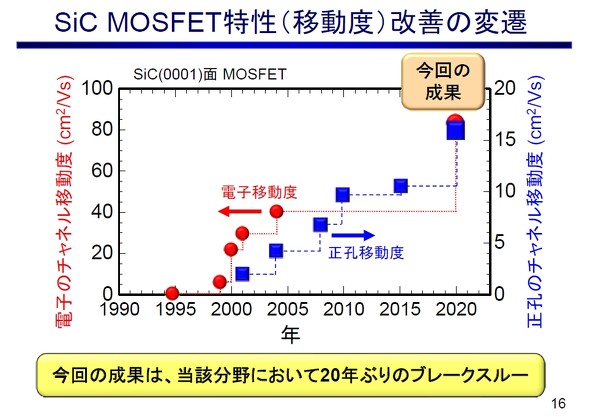

さらに、新手法を用いてn型とp型のSiC-MOSFETを試作したところ、n型では従来比2倍、p型では1.5倍の性能向上を確認した。具体的には、n型でチャネル移動度が40cm2/Vsから85cm2/Vsに、p型では11cm2/Vsから16cm2/Vsになっている。「特に、市場の主流であるn型SiC-MOSFETで性能を2倍にできたので、耐圧600Vや1200VクラスのSiC-MOSFETでは、オン抵抗を25〜35%低減できる。つまり、同じ定格電流を65〜75%のチップサイズで実現できることになり、デバイスのコストを約3割削減できる」(木本氏)

今回はp型SiC-MOSFETも試作して性能向上を確認できたことも大きい。木本氏は「p型MOSFETの性能は、CMOS ICの性能に直結するので、SiCのCMOS ICの開発が本格化した時を見据えると大きな成果を挙げられたのではないか」と語った。

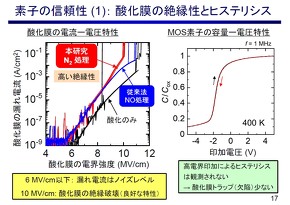

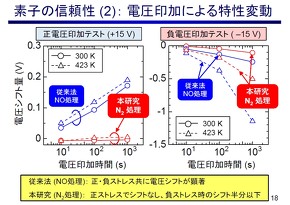

素子の信頼性評価では、酸化膜の絶縁破壊が10MV/cmと良好な特性を確認した他、正電圧印加テスト、負電圧印加テストの両方で、電圧シフト量を従来よりも大幅に抑えられている。

素子の信頼性評価。特に、電圧印加による電圧シフト量が、従来よりも大幅に抑えられている。「今回は、前回よりも過酷な条件での評価結果を見せることができた」と木本氏は述べている 出典:京都大学(クリックで拡大)

素子の信頼性評価。特に、電圧印加による電圧シフト量が、従来よりも大幅に抑えられている。「今回は、前回よりも過酷な条件での評価結果を見せることができた」と木本氏は述べている 出典:京都大学(クリックで拡大)SiC-MOSFETの電子移動度は、NOガスが導入され始めた2000年以降、約20年にわたり大きな向上がなかった。「NOガスの導入条件を調整するくらいのことしかできず、大きく数値を上げることができなかった。今回の成果は20年ぶりのブレークスルーである」(木本氏)

関連記事

新手法の酸化膜形成でSiC-MOSFETの性能が10倍に

新手法の酸化膜形成でSiC-MOSFETの性能が10倍に

SiCパワー半導体で30年来の課題となっていた欠陥の低減が、大きく前進しようとしている。京都大学と東京工業大学(東工大)は2020年8月20日、SiCパワー半導体における欠陥を従来よりも1桁低減し、約10倍の高性能化に成功したと発表した。 新デバイス構造でSiC MOSFETの信頼性を向上

新デバイス構造でSiC MOSFETの信頼性を向上

東芝デバイス&ストレージは、SiC MOSFETの内部にSBDを搭載する新たなデバイス構造を開発した。従来技術に比べて、オン抵抗の上昇を抑えつつSiC MOSFETの信頼性を10倍以上も高めることが可能だという。 パワー半導体世界市場、2025年に243億5100万ドルに

パワー半導体世界市場、2025年に243億5100万ドルに

矢野経済研究所は2020年7月27日、パワー半導体の世界市場予測を発表した。新型コロナウイルス感染症(COVID-19)の影響でパワー半導体の世界市場は2020年にマイナス成長を見せるものの、2021年に一部分野から回復基調に転じ、2025年には243億5100万米ドルにまで成長すると予測している。 25年にトップシェアへ、SiC市場をリードする“後発・ローム”

25年にトップシェアへ、SiC市場をリードする“後発・ローム”

パワー半導体市場に後発として参入しながら、本格的な拡大が見込まれるSiC(炭化ケイ素)パワーデバイス市場において、先進的な研究開発を進めてきたローム。今回、同社取締役 上席執行役員CSO(最高戦略責任者)兼パワーデバイス事業統括の伊野和英氏に話を聞いた。 幅広い製品群をあらゆる用途へ、SiCパワーICにも注力

幅広い製品群をあらゆる用途へ、SiCパワーICにも注力

1927年の創業以来、ヒューズやポリマーPTC、TVSダイオードといった回路保護素子を手掛けてきた米Littelfuse。同社の日本法人であるLittelfuseジャパンでは2020年4月、それまで取締役営業本部長を務めていた亥子正高氏が代表に就任した。同氏に、日本での戦略や、新型コロナウイルス感染症(COVID-19)による影響などを聞いた。 SJ構造を用いたバイポーラトランジスタ開発

SJ構造を用いたバイポーラトランジスタ開発

新日本無線と山梨大学は2020年8月、コレクタ領域をスーパージャンクション構造としたシリコンバイポーラトランジスタ(SJ-BJT)を開発したと発表した。半導体を用いたリレー(ソリッドステートリレー/SSR)の小型化、低損失化が実現できるパワーデバイスだという。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

Special SitePR

あなたにおすすめの記事PR