3D NANDフラッシュの製造コストを2022年まで予測:福田昭のストレージ通信(181) アナリストが語る不揮発性メモリの最新動向(8)(2/2 ページ)

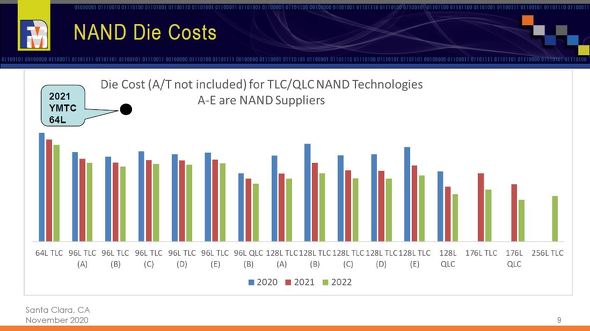

64層から256層までのシリコンダイ製造コストを推定

大手5社の名称は明らかにしていないが、Samsung Electronics、SK hynix、Micron Technology、キオクシア-Western Digital連合、Intelの5社(厳密には4社と1グループ)とみられる。シリコンダイの製造コストには組み立て(パッケージング)コストとテストコストは含まれていない。

2020年の時点でシリコンダイ製造コストをワード線(メモリセル)の積層数で比較すると、96層の世代が最も低いことが分かる。前世代の64層よりも低く、次世代の128層よりも低い。時間の経過に伴う製造コストの減少ペースは128層品が大きく、2021年には大手5社が最小コストで製造する世代は128層となる。

また2021年に登場する176層のTLC品は、ダイコストが128層品と同じかわずかに低い。さらに次の世代である256層のTLC品は2022年に量産が始まる。256層のTLC品はダイコストが当初から、176層のTLC品よりも低くなると予測する。なお中国YMTCが製造する64層品のダイコストは、大手5社に比べて大幅に高い水準にある。

3D NANDフラッシュメモリのシリコンダイ製造コスト推移(組み立てコストとテストコストは含まない)。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)

3D NANDフラッシュメモリのシリコンダイ製造コスト推移(組み立てコストとテストコストは含まない)。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)96層の覇者が、128層でも覇者とは限らない

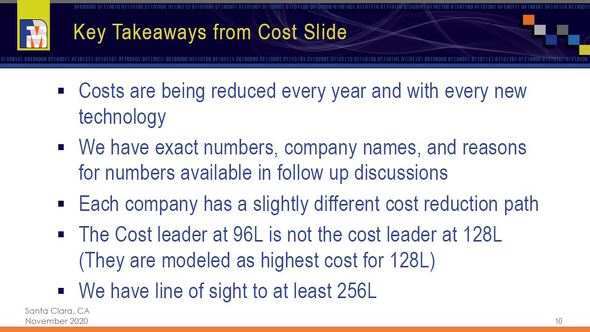

シリコンダイの製造コストは毎年、下がっていく。新しい技術が毎年のように開発され、採用されている。ただし、製造コストを低減していくための要素技術の導入時期は、3D NANDフラッシュのメーカーによって異なる。

3D NANDフラッシュのシリコンダイ製造コストに関するまとめ。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)

3D NANDフラッシュのシリコンダイ製造コストに関するまとめ。出典:FMS 2020の講演「Flash Memory Technologies and Costs Through 2025」の配布資料(クリックで拡大)ここで重要なのは、ある世代で製造コストを最も低くできたメーカーが、次の世代でも製造コストを最も低くできるとは限らないことだ。96層世代の覇者が、128層世代でも勝つかどうかは分からない。技術世代ごとに勝利者が異なる可能性は十分にある。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険