Samsungの埋め込みMRAMをソニーのGPSレシーバーLSIが搭載:福田昭のストレージ通信(196) アナリストが語る不揮発性メモリの最新動向(23)

今回は、Samsung Electronicsが開発した埋め込みMRAM技術の製品化事例を報告する。具体的には、Huaweiのスマートウォッチ「GT2」に搭載されているソニーセミコンダクタソリューションズのGPSレシーバーIC「CXD5605」に、SamsungのMRAMマクロが内蔵されていることが明らかになった。

28nm世代のFD-SOIロジックと互換の埋め込みMRAM

フラッシュメモリとその応用に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」が2020年11月10日〜12日に開催された。FMSは2019年まで、毎年8月上旬あるいは8月中旬に米国カリフォルニア州サンタクララで実施されてきた。COVID-19(新型コロナウイルス感染症)の世界的な大流行(パンデミック)による影響で、2020年のFMS(FMS 2020)は開催時期が3カ月ほど延期されるとともに、バーチャルイベントとして開催された。

FMSは数多くの講演と、展示会で構成される。その中で、フラッシュメモリを含めた不揮発性メモリとストレージの動向に関するセッション「C-9: Flash Technology Advances Lead to New Storage Capabilities」が興味深かった。このセッションは4件の講演があり、その中でアナリストによる3件の講演が特に参考になったので、講演の概要をご紹介する。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第10回から、技術調査会社TechInsightsでシニア技術フェローをつとめるJeodong Choe氏が「Technology Trend:NAND & Emerging Memory(NANDフラッシュメモリと次世代メモリの技術動向)」と題して講演した内容を説明してきた。前々回(第21回)から、代表的な次世代メモリである磁気抵抗メモリ(MRAM)の製品化事例を解説している。前々回はMRAM開発ベンチャーのAvalanche Technologyが開発したスピン注入型磁気抵抗メモリ(STT-MRAM)を米国ルネサスが販売している事例を取り上げた。続いて前回(第22回)は、MRAM開発ベンチャーのEverspin Technologiesが開発してきた3世代のMRAM技術を解説した。

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)今回は、半導体メモリ大手メーカーのSamsung Electronics(以降はSamsungと表記)が開発した埋め込みMRAM技術の製品化事例をご報告する。SamsungはSoC(System on a Chip)やマイクロコントローラー(マイコン)などの埋め込みフラッシュメモリ(eFLASH)を置き換えることを想定した埋め込みMRAM(eMRAM)技術を開発してきた。2019年3月には、28nm世代のFD-SOI CMOSロジックと互換のeMRAMマクロの量産を始めたと公式に発表している(参考記事:「Samsung、28nm FD-SOIプロセス適用のeMRAMを出荷へ」)。

磁気トンネル接合(MTJ)を第6層と第7層の配線間に作り込む

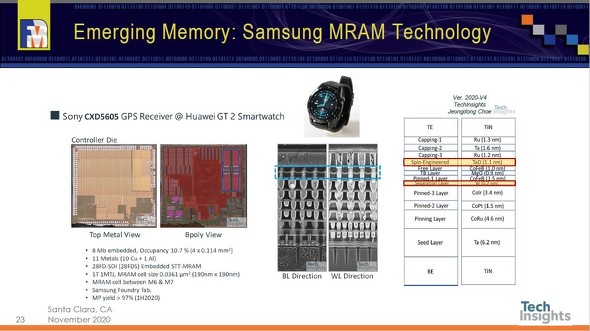

技術調査会社TechInsightsは、中国Huaweiのスマートウォッチ「GT2」を分解してソニーセミコンダクタソリューションズのGPSレシーバーLSI(GNSS受信LSI)「CXD5605」を取り出し、シリコンダイを分析した。Choe氏は講演で、「CXD5605」のシリコンダイはSamsungが28nm世代のFD-SOI CMOSロジック技術によって製造しており、Samsungが提供した埋め込みMRAM(eMRAM)マクロを内蔵していることを明らかにした。

Huaweiのスマートウォッチ「GT2」からソニーのGPSレシーバーIC(GNSS受信LSI)「CXD5605」を取り出し、シリコンダイを分析した結果。Samsungが28nm世代のFD-SOI CMOS技術で製造した。8MビットのSTT-MRAMマクロを内蔵している。左側の2枚はシリコンダイの撮影画像、中央の2枚はMRAMマクロの断面を電子顕微鏡で観察した画像。右側は磁気トンネル接合(MTJ)の構造図。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

Huaweiのスマートウォッチ「GT2」からソニーのGPSレシーバーIC(GNSS受信LSI)「CXD5605」を取り出し、シリコンダイを分析した結果。Samsungが28nm世代のFD-SOI CMOS技術で製造した。8MビットのSTT-MRAMマクロを内蔵している。左側の2枚はシリコンダイの撮影画像、中央の2枚はMRAMマクロの断面を電子顕微鏡で観察した画像。右側は磁気トンネル接合(MTJ)の構造図。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)eMRAMの記憶容量は8Mビットである。メモリセルは1個のセル選択用MOSFETと1個の磁気トンネル接合(MTJ)で構成する。「1T1R」と呼ばれる標準的なメモリセルだ。MTJは第6層金属配線(M6)と第7層金属配線(M7)の間に作り込んだ。MTJの層数は上下電極層を除くと12層とかなり多い。メモリセル面積は0.0361μm2(190nm角)とあまり小さくはない。磁気記録方式はスピン注入と垂直磁気記録の組み合わせ(pSTT方式)である。

GPSレシーバーLSI「CXD5605」のシリコンダイに占めるeMRAMマクロの割合は10.7%。eMRAMマクロの面積は4mm×0.114mmである。ここから逆算すると「CXD5605」のシリコンダイ面積は4.26mm2(正方形の場合は2.064mm角)となり、かなり小さい。製造技術は28nm世代のFD-SOI CMOSロジック技術と11層の金属配線(10層の銅配線と1層のアルミニウム配線)技術である。シリコンダイの製造はSamsungが担当した。製造歩留まりは2020年上半期の時点で97%以上とかなり高い。なおソニーの「CXD5605」に関する製品仕様では、動作温度範囲は−40℃〜+85℃となっている。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険