Samsungが次世代2.5D実装技術「I-Cube4」を発表:ロジックと4個のHBMを積層

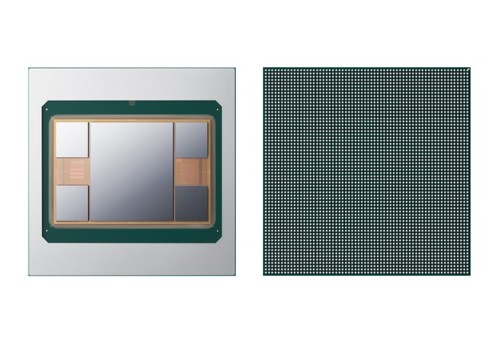

Samsung Electronics(以下、Samsung)は2021年5月6日(韓国時間)、2.5D(2.5次元)パッケージング技術「I-Cube4」(Interposer-Cube4/アイキューブ4)の提供を開始したと発表した。

Samsung Electronics(以下、Samsung)は2021年5月6日(韓国時間)、2.5D(2.5次元)パッケージング技術「I-Cube4」(Interposer-Cube4/アイキューブ4)の提供を開始したと発表した。

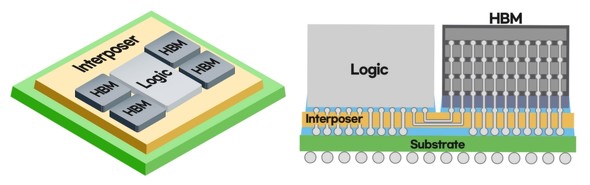

Samsungの「I-Cube」は、1個または複数個のロジックダイとHBM(High Bandwidth Memory)ダイを、シリコンインターポーザー上に積層する実装技術。これにより、複数のダイを1チップとして、1パッケージに搭載することができる。

I-Cube4は、1個のロジックダイと4個のHBMダイを積層したもので、HPC(High Performance Computing)からAI(人工知能)、5G(第5世代移動通信)、大規模データセンター向けチップへの適用を目指す。

インターポーザーの面積は、ロジックダイやHBMダイの個数が増加するとそれに伴って増加する。I-Cubeで使われるインターポーザーの厚さは100μmと紙よりも薄いため、インターポーザ―の面積が大きくなると、曲がってしまい、チップの質に悪影響を与える可能性があるという。Samsungは、材料や厚さを変えることで、インターポーザ―の反りや熱膨張を制御する方法を研究し、I-Cube4の実用化に成功したと説明する。

さらに、効率的に放熱できるよう、I-Cube4向けに独自のモールドフリー構造を開発した。

Samsungは2018年に「I-Cube2」、2020年に「X-Cube(eXtended-Cube)」を発表している。I-Cube2は1個のロジックダイと2個のHBMダイを集積する技術で、X-CubeはロジックダイとSRAMを垂直に積層する技術である。

関連記事

2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

今回は、「IEDM2020」から先端パッケージの講演をいくつか紹介する。そこで見えてきたのは、今後「ムーアの法則」のけん引役となるかもしれない「チップレット」技術と、その開発競争が進んでいるということだった。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 Intelの高性能・高密度パッケージング技術「EMIB」の概要

Intelの高性能・高密度パッケージング技術「EMIB」の概要

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。 TSMCが90億ドルの資金調達へ、日本に子会社設立も

TSMCが90億ドルの資金調達へ、日本に子会社設立も

TSMCは、生産を拡大すべく、2種類の債権売却によって約90億米ドルの資金を調達する予定であると発表した。深刻な半導体チップ不足を解消していきたい考えだという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増