フォークシート構造のトランジスタが次世代以降の有力候補である理由:福田昭のデバイス通信(305) imecが語る3nm以降のCMOS技術(8)(2/2 ページ)

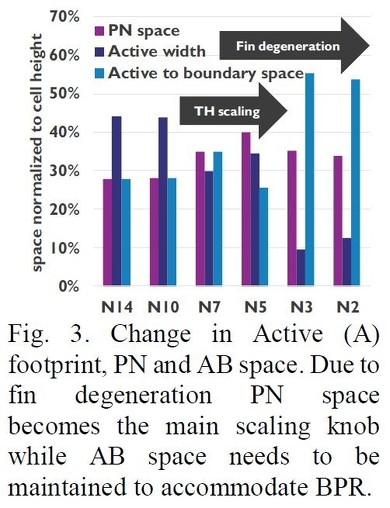

続いて基本セルの高さ(CH)に占める各部の寸法をCMOSロジックの技術ノードごとに検討する。14nm世代(N14)と10nm世代(N10)では、CHの約4割強を「A」が占めており、「PN」と「AB」はいずれも3割弱という配分だった。それが7nm世代(N7)では、「A」の割合が約3割に減少し、「PN」と「AB」がいずれも3割強に増加した。続く5nm世代(N5)では「PN」の割合がさらに増えて4割となり、一方で「AB」は2割5分前後へと減る。「A」の割合は逆に3割5分前後へと上昇する。

基本セルの高さ(CH)に占める各部の割合と技術ノード(N)の推移。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)

基本セルの高さ(CH)に占める各部の割合と技術ノード(N)の推移。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)3nm世代(N3)以降では、BPR技術の導入によって「AB」の割合が5割超と最も大きくなる。この割合はあまり変えられない。「A」の割合は1割前後へと大きく減る。一方で「PN」は、3割5分前後とかなりの比率を占める。すなわちN5以降は「PN」を短くすることが、微細化の大きなカギとなる。

このような微細化シナリオから、「PN」を短くできる「フォークシート構造」が「ナノシート構造」よりも有利であるというのが、imecの主張だ。

フォークシート構造はセルレイアウトの自由度が高い

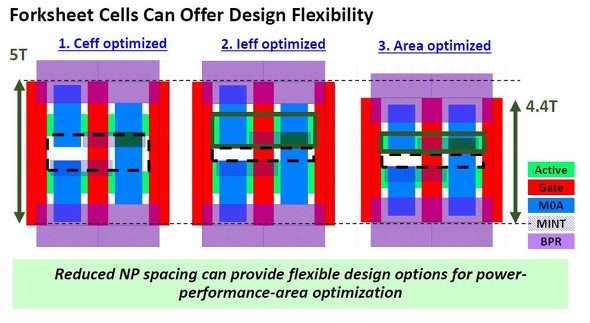

フォークシート構造には、セルレイアウトの自由度が高いという特長もある。「PN」と「A」の両方を制御できるからだ。講演では、寄生容量を最小化したレイアウト、電流駆動能力を最大化したレイアウト、セル面積を最小化したレイアウトを示していた。

寄生容量を最小化したレイアウトではアクティブ領域をあまり太くせず、トランジスタ間の距離を適度に確保した。電流駆動能力を最大化したレイアウトでは、アクティブ領域を太くするとともにトランジスタ間の距離を詰めた。セル面積を最小化したレイアウトではアクティブ領域を細くし、トランジスタ間の距離を詰めている。セルの高さを4.4Tと低く抑えた。

フォークシート(Forksheet)構造で基本セルのレイアウトを最適化した例。左は寄生容量を最小化したレイアウト、中央は電流駆動能力を高めたレイアウト、右はセル面積を最小化したレイアウト。なお図中の「M0A」は「Contact-to-Active, Active Trench Contact(アクティブ層につながるコンタクト金属層)」、「MINT」は「水平方向の最下層金属配線(一般的にはM1に相当)」、「BPR」は「Buried Power Rail(埋め込み電源/接地線)」を意味する。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

フォークシート(Forksheet)構造で基本セルのレイアウトを最適化した例。左は寄生容量を最小化したレイアウト、中央は電流駆動能力を高めたレイアウト、右はセル面積を最小化したレイアウト。なお図中の「M0A」は「Contact-to-Active, Active Trench Contact(アクティブ層につながるコンタクト金属層)」、「MINT」は「水平方向の最下層金属配線(一般的にはM1に相当)」、「BPR」は「Buried Power Rail(埋め込み電源/接地線)」を意味する。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増