論理回路セルとSRAMセルを縮小するフォークシート構造:福田昭のデバイス通信(307) imecが語る3nm以降のCMOS技術(10)(1/2 ページ)

今回は基本的な論理回路セルとSRAMセルで、FinFETとナノシート構造、フォークシート構造のシリコン面積がどのくらい変化するかを説明する。

FinFET、ナノシート構造と回路ブロックの面積を比較

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。第298回から「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。第298回から「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している(クリックで拡大)本シリーズの第6回から、2番目のパートである「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している。同回は、FinFET(フィンフェット)をトランジスタとするCMOSロジックの微細化限界と限界突破策の候補である「ナノシート(Nanosheet)構造」を説明した。続く第7回は、ナノシート構造だと微細化を継続して進められない理由と、解決策としての「フォークシート(Forksheet)構造」を紹介した。そして第8回は、フォークシート構造がどのような利点を備えているかを基本セルの高さと微細化の関係から説明した。第9回(前回)は、フォークシート構造のトランジスタ対(pチャンネルとnチャンネル)を製造する工程を述べるとともに、試作したトランジスタ対の断面を観察および分析した結果を示した。

今回は基本的な論理回路セルとSRAMセルで、FinFETとナノシート構造、フォークシート構造のシリコン面積がどのくらい変化するかを説明する。

フォークシート構造はFinFETに比べてレイアウトの自由度が上がる

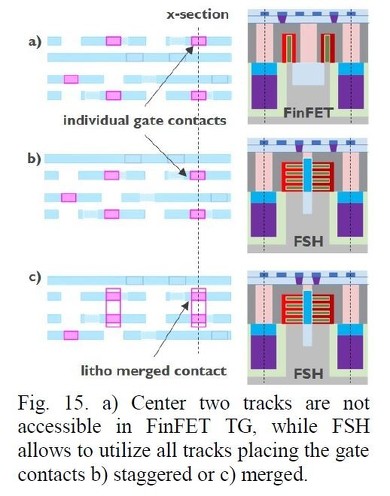

論理回路セルではFinFETに比べ、フォークシート構造のCMOSロジックはレイアウトの自由度が上がる。具体的には、FinFETのCMOSインバーターはトラック(水平方向に走る最下層金属配線)とゲートを接続するコンタクトの位置に制限が加わる。中央の2トラックにはコンタクトを作れない。しかしフォークシート構造だと、中央の2トラックにもコンタクトを配置できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- 東芝との協議やデンソー提案への対応、ロームが新声明

- デンソー、ロームに対する株式取得提案を正式表明

- キオクシアが超高IOPS SSD開発 NVIDIA Storage-Nextに対応

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- STが「中国製STM32」量産開始、供給網を現地完結

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表