ナノシート構造を超える高い密度を実現するフォークシート構造のトランジスタ:福田昭のデバイス通信(304) imecが語る3nm以降のCMOS技術(7)

前回に続き、「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介する。imecは、フォークシート構造のトランジスタの研究開発に力を入れている。

ナノシート構造の長所と短所

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している(クリックで拡大)本シリーズの前回から、2番目のパートである「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介している。前回は、FinFET(フィンフェット)をトランジスタとするCMOSロジックの微細化限界と限界突破策の候補である「ナノシート構造」を説明した。

FinFETでCMOSロジックの基本セル(スタンダードセル)を縮小するためには、フィンのピッチを詰める、フィンの枚数を減らす、フィンを薄くする、フィンを高くするといった手法を採らざるを得ない。すると、FinFETのフィン当たりの電流駆動能力を高めつつ、フィンごとのばらつきを縮小する必要が生じる。この課題は微細化とともに難しさを増す。

そこで考案されたのが、FinFETのフィンを真横に倒したようなチャンネル構造(「ナノシート(Nanosheet)構造」)のトランジスタである。ナノシート構造のトランジスタ(「ナノシート・トランジスタ」あるいは「NSHトランジスタ」とも呼ぶ)は電流駆動能力が高い、ばらつきが少ないといった特長を備える。しかしimecはナノシート構造の開発にはあまり積極的ではないようだ。ナノシート構造はトランジスタ間の素子分離に、FinFETと同等以上の距離を必要とするというのが、その主な理由である。

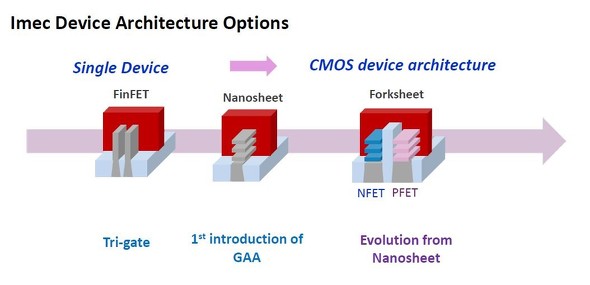

FinFETからナノシート(Nanosheet)構造、さらにはフォークシート(Forksheet)構造への変革。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

FinFETからナノシート(Nanosheet)構造、さらにはフォークシート(Forksheet)構造への変革。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)imecが推すのは、「フォークシート(Forksheet)構造」と呼ぶチャンネル構造のトランジスタ(「フォークシート・トランジスタ」あるいは「FSHトランジスタ」とも呼ぶ)である。ナノシート構造を基本に重要な改良を施すことで、トランジスタ間の距離を詰められるようにした。2nm以降の世代では、フォークシート構造がトランジスタ技術の有力な候補だとする。

トランジスタ間の距離を極限までに詰められるフォークシート構造

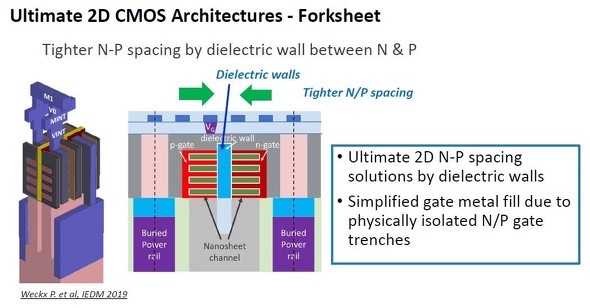

フォークシート構造では、絶縁膜の薄い壁を挟んでpチャンネルのナノシートとnチャンネルのナノシートが対を成す。ゲート金属の断面構造が食器のフォークに似た形状となるので、「フォークシート」と呼ぶ。

フォークシート構造では、隣接するチャンネルとゲート金属は物理的に分離されている。このため、隣接するトランジスタ間の距離を極限にまで詰められる。すなわちCMOSロジックの基本セルを小さくできる。

フォークシート(Forksheet)構造でpチャンネルとnチャンネルのトランジスタを作り込む模式図。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

フォークシート(Forksheet)構造でpチャンネルとnチャンネルのトランジスタを作り込む模式図。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)さらに、フォークシート構造にはナノシート構造に比べて寄生容量が小さいという利点がある。フォークシート構造のトランジスタは同じ消費電力だとナノシート構造に比べて高速に動作する。逆の表現をすると、同じ動作周波数ではフォークシート構造はナノシート構造に比べて消費電力が低くなる。国際学会IEDM2019でimecが発表した論文(論文番号36.5)によると、CMOSインバーターの15段リング発振器で比較したところ、動作周波数(同じ消費電力で比較)はフォークシート構造が10%向上し、消費電力(同じ動作周波数で比較)はフォークシート構造が24%減少した。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

電源供給配線網(PDN)をシリコンダイの裏面に配置して電源をさらに安定化

電源供給配線網(PDN)をシリコンダイの裏面に配置して電源をさらに安定化

今回は、CMOSロジックの基本セル(スタンダードセル)に電源を分配する電源供給配線網(PDN:Power Delivery Network)のレイアウトを解説する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 21Q1の半導体売上高は前四半期比増に、2010年以来初

21Q1の半導体売上高は前四半期比増に、2010年以来初

英市場調査会社であるOmdiaは2021年6月14日(現地時間)、同年第1四半期(1〜3月期)における半導体市場の売上高が1313億米ドルとなり、2020年第4四半期に比べて0.5%増加したと発表した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増