EE Times Japan >

LSI >

論理回路セルとSRAMセルを縮小するフォークシート構造:福田昭のデバイス通信(307) imecが語る3nm以降のCMOS技術(10)(2/2 ページ)

» 2021年07月05日 11時30分 公開

[福田昭,EE Times Japan]

データ型フリップフロップ(D-FF)の面積はナノシート構造から2割低減

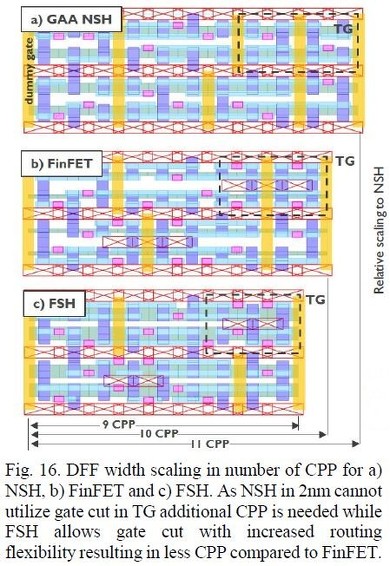

続いてデータ型フリップフロップ(D-FF)の論理回路セルを比較しよう。同じ高さのセルで、コンタクトゲートピッチ(CPPあるいはCGP)の数に違いが生じる。ナノシート(NSH)構造では11ピッチ、FinFETでは10ピッチ、フォークシート(FSH)構造では9ピッチとなる。FSH構造のD-FFは、セル面積がNSH構造に比べて2割ほど小さくなっていることが分かる。

データ型フリップフロップ(D-FF)のセルレイアウト。上からナノシート(GAA NSH)構造(a)、FinFET(b)、フォークシート構造(c)。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)

データ型フリップフロップ(D-FF)のセルレイアウト。上からナノシート(GAA NSH)構造(a)、FinFET(b)、フォークシート構造(c)。出典:2019年12月にIEDM2019でimecが発表した論文「Novel forksheet device architecture as ultimate logic scaling device towards 2nm」(論文番号36.5)から(クリックで拡大)SRAMセル面積はナノシートと比べて2割〜3割縮小

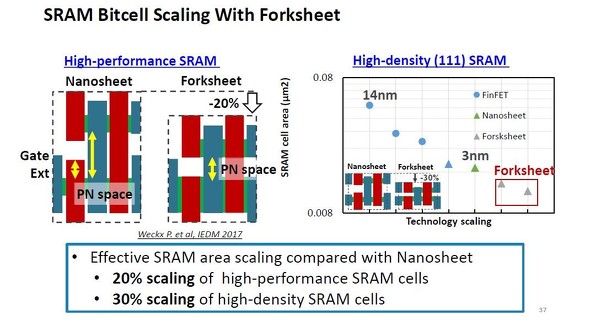

SRAMセルは高性能タイプのレイアウトと、高密度タイプのレイアウトでそれぞれナノシート構造とフォークシート構造を比較した。

高性能タイプのSRAMセルでは、フォークシート構造がpチャンネルとnチャンネルの距離(PN)を短く詰められることから、セル面積を約2割、小さくできる。高密度タイプのSRAMセルだと、同様にセル面積を約3割、低減できる。

SRAMセルの面積をナノシート構造とフォークシート構造で比較。左は高性能タイプのSRAMセル。右は高密度タイプのSRAMセル。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

SRAMセルの面積をナノシート構造とフォークシート構造で比較。左は高性能タイプのSRAMセル。右は高密度タイプのSRAMセル。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR