EE Times Japan >

LSI >

FinFETの「次の次」に来るトランジスタ技術:福田昭のデバイス通信(308) imecが語る3nm以降のCMOS技術(11)(2/2 ページ)

» 2021年07月09日 10時30分 公開

[福田昭,EE Times Japan]

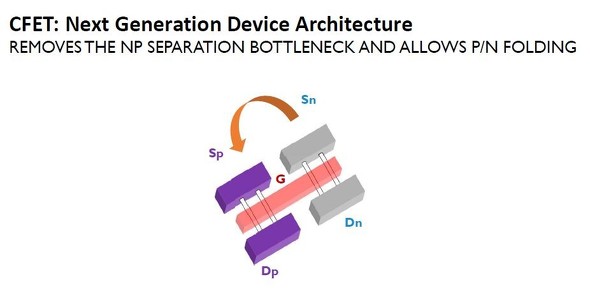

pチャンネルにnチャンネルのトランジスタを重ねる3次元構造

CFETの考え方は単純だ。平面状のpチャンネルMOSFETとnチャンネルMOSFETで構成されるCMOSインバーターは、細長いゲート電極を共有する。ここでゲート電極の中央を区切りとして2つのトランジスタを折りたたむ。pチャンネルFETの上にnチャンネルFETを重ねた3次元(3D)積層構造のトランジスタ対となる。

pチャンネルFETが下になるのは、製造工程としては先にpチャンネルFETを作り、後でnチャンネルFETを作るという順番が標準的なことによる。原理的にはnチャンネルFETを下にしてもCFETを作れる。

「コンプリメンタリFET(C(Complementary)FET)」の考え方。Sはソース、Dはドレイン、Gはゲートである。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

「コンプリメンタリFET(C(Complementary)FET)」の考え方。Sはソース、Dはドレイン、Gはゲートである。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)2nm以降の技術世代でトランジスタの候補となる

CFETの特徴をあらためて述べるとまず、CMOS基本セルの縮小がある。従来のトランジスタ回路に比べてシリコン面積が約半分に減る。2個のトランジスタで構成するCMOSデバイスを、1個のトランジスタに近いシリコン面積で作れる。またゲートのピッチをあまり詰めずに済む。さらには、pチャンネルの材料とnチャンネルの材料を独立に選べる。

「コンプリメンタリFET(C(Complementary)FET)」の特徴と、試作したトランジスタの断面構造を電子顕微鏡で観察した画像。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond ‐ device architectures, parasitics and materials」の配布資料) (クリックで拡大)

「コンプリメンタリFET(C(Complementary)FET)」の特徴と、試作したトランジスタの断面構造を電子顕微鏡で観察した画像。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond ‐ device architectures, parasitics and materials」の配布資料) (クリックで拡大)CFETがCMOSロジックの有力候補となるのは、2nm以降の技術世代である。1.5nm世代あるいは1.0nm世代で、CFETが必要になるとみられる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

NVMe 2.0、「未来のストレージの需要に対応」

NVMe 2.0、「未来のストレージの需要に対応」

SSD接続規格である「NVMe(Non-Volatile Memory express)」が次のレベルへと移行する準備を整えつつある。NVM Expressは2021年6月、「NVMe 2.0」の仕様を発表した。 異種デバイスの融合を実現する3次元集積化技術

異種デバイスの融合を実現する3次元集積化技術

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- ヒューマノイドはどこまで現実になっているのか

Special SitePR

あなたにおすすめの記事PR