次々世代のトランジスタ技術「コンプリメンタリFET」の構造と種類:福田昭のデバイス通信(310) imecが語る3nm以降のCMOS技術(13)

今回はCFETのトランジスタ構造と、CFETは製造方法の違いによって2種類に分けられることを説明する。

チャンネルの構造はフィンとナノシートの両方が使える

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前々回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前々回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)前々回から、3番目のパートである「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している。同回は、「コンプリメンタリFET(C(Complementary)FET)」の基本的な概念と、期待できる利点を説明した。前回はCFETのトランジスタ構造がCMOS基本セル(スタンダードセル)の微細化に与えるメリットを解説した。今回はCFETのトランジスタ構造を述べるとともに、CFETは製造方法の違いによって2種類に分けられることを説明する。

始めはCFETの断面構造を述べよう。最下層にBPR(Buried Power Rail)技術による埋め込み電源配線(VDD)と埋め込み接地配線(VSS)があり、その上にpチャンネルMOSFET(pFET)のチャンネル(フィンあるいはナノシート)、それからコンタクト電極(ボトム電極)がくる。pFETと埋め込み電源配線(VDD)がビアを介して接続される。

ボトム電極の上には、nチャンネルMOSFET(nFET)のチャンネル(フィンあるいはナノシート)があり、チャンネルを囲むようにコンタクト電極(トップ電極)がくる。ボトム電極とトップ電極はビアを介して第0層金属配線(M0)につながる。

CFETの断面構造(左)と鳥瞰図(右)。出典:imecが2019年12月に国際学会IEDMで発表した論文「Enabling Sub-5nm CMOS Technology Scaling Thinner and Taller!」(論文番号29.4)から(クリックで拡大)

CFETの断面構造(左)と鳥瞰図(右)。出典:imecが2019年12月に国際学会IEDMで発表した論文「Enabling Sub-5nm CMOS Technology Scaling Thinner and Taller!」(論文番号29.4)から(クリックで拡大)ここで重要なのは、CFETはチャンネルの構造とは別の概念であることだ。例えばpFETがFin(フィン)FET、nFETがナノシート構造といった選択肢が十分にあり得る。

モノリシック製造とシーケンシャル製造

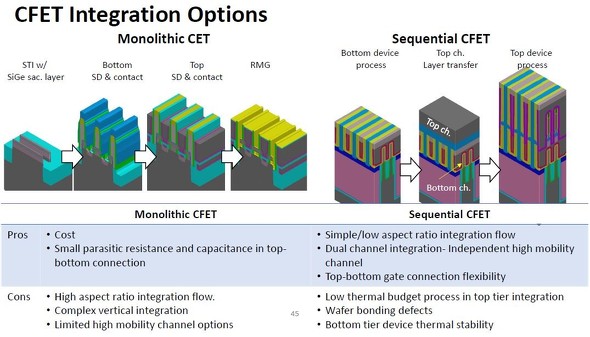

CFETの製造方法は大きく分けると2種類ある。1つは、成膜工程やエッチング工程、拡散工程などを繰り返して2つのトランジスタを垂直に積み上げる方法である。「モノリシック(Monolithic)CFET」と呼ぶ。もう1つは、下側(底側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側)のトランジスタを製造する方法である。「シーケンシャル(Sequential)CFET」と呼ぶ。

「モノリシック(Monolithic)CFET」(左)と「シーケンシャル(Sequential)CFET」(右)の概要。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

「モノリシック(Monolithic)CFET」(左)と「シーケンシャル(Sequential)CFET」(右)の概要。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)モノリシックCFETの利点は、製造コストが低いこと、上下のトランジスタを電気的に接続する部分の寄生素子(抵抗と静電容量)が小さいことだ。弱点は、高いアスペクト比の微細加工を必要とすること、垂直方向の積み上げプロセスが複雑であること、チャンネルの材料を選べないこと(化合物半導体といった高移動度材料を採用できないこと)、である。

シーケンシャルCFETの利点は、製造プロセスが比較的簡素であり、高いアスペクト比の加工が不要であること、チャンネルの材料を選べる(高移動度材料を利用できる)こと、上側と下側のゲート電極の接続レイアウトがかなり自由であることだ。弱点は、上側のトランジスタを形成するプロセスを比較的低い温度にとどめる必要があること、ウエハーの貼り合わせによる欠陥が発生する恐れがあること、下側のトランジスタが高温プロセスによって不安定になる恐れがあること、である。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

RVVプロセッサで初めてASIL D Ready認証を取得

RVVプロセッサで初めてASIL D Ready認証を取得

RISC-V Vector Extension(RVV)を実装したエヌエスアイテクス製のDFP(Data Flow Processor)「DR1000C」が、SGS-TUVから「ISO 26262 ASIL D Ready」の認証を取得した。「RVVプロセッサでは初めての認証取得」だという。 清華紫光集団が破産を認める、企業再編へ

清華紫光集団が破産を認める、企業再編へ

債務超過に陥っている中国の半導体企業「Tsinghua Unigroup(清華紫光集団)」が、破産を認めた。3D NAND型フラッシュメモリベンチャーである YMTC(Yangtze Memory Technologies Corporation)や半導体設計を手掛けるUnisoc(Shanghai)Technologiesなどの半導体メーカーを傘下に持つ中国の持株会社である同社は、企業再編を進めることを明らかにした。 6000DMIPSの性能でリアルタイム制御に強いマイコン

6000DMIPSの性能でリアルタイム制御に強いマイコン

Texas Instruments(TI)の日本法人である日本テキサス・インスツルメンツ(日本TI)は2021年7月12日、FA(ファクトリーオートメーション)やロボット、車載システムなどの用途に向けて、新しいマイコン(MCU)シリーズ「Sitara AM2x」を発表した。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待