次々世代のトランジスタ「モノリシックCFET」の製造プロセス:福田昭のデバイス通信(311) imecが語る3nm以降のCMOS技術(14)

今回から、2種類のCFETの製造プロセスを解説していく。始めは「モノリシックCFET」を取り上げる。

コンプリメンタリFET(CFET)を製造する2つの方法

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第11回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第11回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)本シリーズの第11回から、3番目のパートである「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している。前回(第13回)では、「コンプリメンタリFET(C(Complementary)FET)」は製造方法の違いによって2種類に分けられると述べた。

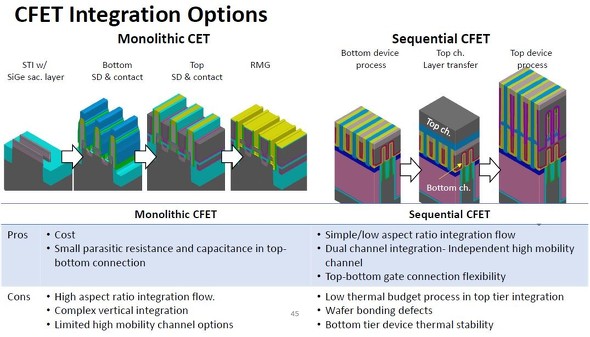

1つは、「モノリシック(Monolithic)CFET」と呼ぶ。成膜工程やエッチング工程、拡散工程などを繰り返して2つのトランジスタを積み上げる方法である。もう1つは、「シーケンシャル(Sequential)CFET」と呼ぶ。下側(底側、ボトム側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側、トップ側)のトランジスタを製造する方法である。

「モノリシック(Monolithic)CFET」(左)と「シーケンシャル(Sequential)CFET」(右)の概要。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

「モノリシック(Monolithic)CFET」(左)と「シーケンシャル(Sequential)CFET」(右)の概要。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)今回から、2種類のCFETの製造プロセスを述べていく。始めは「モノリシックCFET」を扱う。

モノリシック製造のカギは垂直な柱の壁面を平らに形成すること

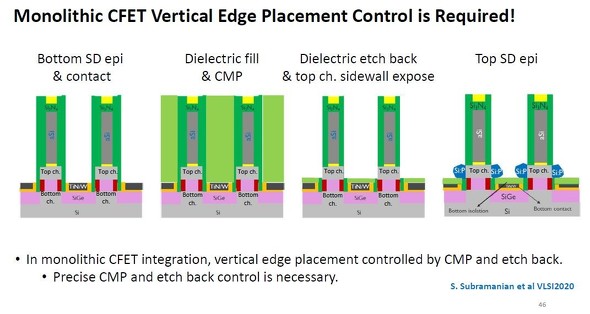

モノリシックCFETの製造プロセスは以下のように進む。始めはボトム側トランジスタのチャンネルとゲート電極、トップ側トランジスタのチャンネルとゲート電極を積層していく。次にボトム側の拡散層(ソースとドレイン)とコンタクト電極を形成する。それから全体に誘電体絶縁膜を満たし、CMP(Chemical Mechanical Polishing)によって平坦化する。続いてエッチングによって誘電体絶縁膜を除去するとともに、積層構造のシリコン窒化(Si3N4)膜(絶縁膜)を削り、トップ側のチャンネル側壁を露出させる。

ここで重要なのは、CMPとエッチングの精密な制御だ。シリコン窒化膜の側壁とチャンネルの側壁をきれいな平面で露出させることが求められる。 それから、トップ側のチャンネル側壁に拡散層(ソースとドレイン)をエピタキシャル成長する。

モノリシック(Monolithic)CFETの製造工程(一部のみ)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

モノリシック(Monolithic)CFETの製造工程(一部のみ)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)講演では、ボトム側のpチャンネルFinFETとトップ側のnチャンネル・ナノシートFETを個別に試作した結果を示していた。いずれのトランジスタも、ゲート電圧によってドレイン電流を104倍以上に変化させることができた。両者をモノリシック集積することが、今後の課題だ。

試作したCFETの断面構造(電子顕微鏡による観察画像)と静特性。上がトップ側のnチャンネルFET(ナノシート構造)、下がボトム側のpチャンネルFET(フィン構造)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

試作したCFETの断面構造(電子顕微鏡による観察画像)と静特性。上がトップ側のnチャンネルFET(ナノシート構造)、下がボトム側のpチャンネルFET(フィン構造)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

コンプリメンタリFET(CFET)でCMOS基本セルの高さを半分に減らす

コンプリメンタリFET(CFET)でCMOS基本セルの高さを半分に減らす

引き続き、FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET/CFET)の講演部分を紹介する。今回は、CFETがCMOS基本セルの微細化に与えるメリットを具体的に解説する。 GFがニューヨーク州に新工場建設へ

GFがニューヨーク州に新工場建設へ

GLOBALFOUNDRIES(GF)は2021年7月19日(米国時間)、ニューヨーク州マルタのキャンパス内に、工場を新設すると発表した。今後数年間に及ぶ生産能力の拡張計画の一環で、工場新設と、本社のある既存工場「Fab 8」への投資が含まれる。新工場が完成すると、マルタの工場の敷地面積は2倍になる予定だ。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」