堅調に成長するCXLエコシステム:新製品も続々登場(2/2 ページ)

RambusのCXL Memory Interconnect Initiative

メモリはCXL製品にとって唯一の可能性ではない。CXLコンソーシアムのメンバーであるMicrochip Technologyは、いち早くCXL 2.0リタイマー「XpressConnect」を発表した。このリタイマーは、AIや機械学習などコンピューティング作業負荷のサポートに必要な超低遅延の信号伝送に対応することで、データセンターの作業負荷が抱える高性能コンピューティングの需要に対処する製品だ。

一般的にPCIeリタイマーは、PCIeバスの長さを延長するためのICとしてPCB上に実装される。リタイマーは、インターコネクトやPCB、ケーブルの変更などにより劣化した信号を、きれいな状態に再生成して出力する。

Rambusにとって、CXLは単なるメモリプールのためのものではない。同社は、CXLによって自社のIPを囲い込み、最近立ち上げたイニシアチブ「CXL Memory Interconnect Initiative」を加速させようとしている。そうして、データセンターの進化するアーキテクチャや、サーバ作業負荷の継続的な成長や専門化をサポートすることを狙っているのだ。

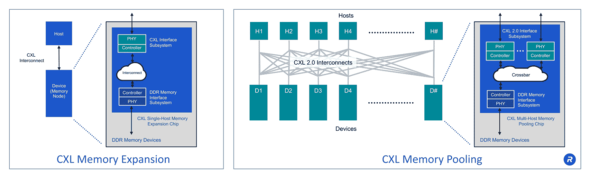

CXLメモリの拡張により、ホスト(CPU)に提供されるメインメモリが増え、大容量のワークロードで高いパフォーマンスを発揮、CXLメモリのプール化によって、最終的にディスアグリゲーションやコンポーザビリティをサポートする 出典:Rambus

CXLメモリの拡張により、ホスト(CPU)に提供されるメインメモリが増え、大容量のワークロードで高いパフォーマンスを発揮、CXLメモリのプール化によって、最終的にディスアグリゲーションやコンポーザビリティをサポートする 出典:RambusRambusのIPコア担当ゼネラルマネジャーのMatt Jones氏は、「CXLおよびPCIeデジタルコントローラーを提供する米PLDAと、PHYを提供するカナダのAnalogXを買収したことで、サーバ用メモリインタフェースチップに関する当社の専門性を補完する製品と専門知識が加わった」と述べる。基本的に同社のIPは、メモリと、SerDesインタフェースを含むチップ間側のデータ伝送という2つに分けられる。「今回の買収は、このイニシアチブに合致している」(同氏)

Jones氏は、「Rambusは、データセンターの新しいアーキテクチャが、サーバというコンピューティングの単位から、さまざまなワークロードのニーズに合わせてコンピューティングリソースを“構成”できるような分散型モデルに移行すると考えている」と説明する。デバイスの拡張やプール化は、同社が以前から検討していたものだ。

Jones氏によれば、CXL Memory Interconnect Initiativeは、

- CXL、PCIe PHYおよび、ホストプロセッサやその他のデバイスと接続するためのコントローラー

- DDRメモリPHYおよび、メモリデバイスと接続するためのコントローラー

- ファームウェアの安全なダウンロードを可能にし、データの改ざんや物理的な攻撃からリンクを保護するIntegrity and Data Encryption(IDE)セキュリティを備えた高度な暗号コアとセキュアなプロトコルエンジン

といった、さまざまなビルディングブロックをまとめているという。

RambusフェローのSteve Woo氏は、「Rambusは、データセンターのアーキテクチャの進化に伴って必要となる半導体やデータパスの安全性を確保することを目指しており、過去10年間に行った企業買収が当社のCXL戦略の一翼を担っている」と語った。

その他の技術としては、DIMM(Dual Inline Memory Module)に取り付けられ、ホストプロセッサと実際のDRAMの間に配置されるバッファーチップがある。同氏は、「われわれは、チップビジネスと、CPUと実際のメモリデバイスの間のバッファーで何かを行うための構成要素を全て備えた、非常に優れたポートフォリオを持っている」と説明している。

Woo氏は、「新しいデータアーキテクチャは、コンピューティングがもはやボトルネックではないことを反映している」と語る。CXLでは、サーバ筐体の外側に大きなメモリプールがあり、必要に応じてプロビジョニングを行い、ワークロードが完了したときに戻すことができる。「CXLは、データとデータのやりとりだけに関わるものだ。設計者は、CPUにそれほど依存しないメモリを探している」(同氏)

【翻訳:青山麻由子、編集:EE Times Japan】

関連記事

「Optane」導入加速を支えるエコシステム

「Optane」導入加速を支えるエコシステム

現在、「3D XPoint」メモリの分野では、Intelの「Optane」だけが唯一の選択肢であるため、3D XPointの導入を加速し、エコシステムを構築していくには、プレイヤーたちにサポートを提供する必要がある。 Micronが「3D XPoint」開発から撤退へ、工場も売却

Micronが「3D XPoint」開発から撤退へ、工場も売却

Micron Technology(以下、Micron)は2021年3月16日(米国時間)、同社がIntelと共同開発した不揮発メモリ「3D XPoint」の開発から撤退し、CXL(Compute Express Link)を用いる新しいメモリ製品への開発へとリソースを移行すると発表した。 「CXL」がさらに進化、バージョン2.0を発表

「CXL」がさらに進化、バージョン2.0を発表

オープンな業界標準インターコネクト規格「Compute Express Link(CXL)」が、安定したペースで前進し続けている。今回、始動当初から2年もたたないうちに、次世代版「CXL 2.0」が発表された。CXLコンソーシアムのメンバー企業は既に、このCXL 2.0を適用した製品をリリースしているという。 AI新興企業への投資を拡大するIntel

AI新興企業への投資を拡大するIntel

Intelの投資部門であるIntel Capitalは、技術新興企業向けの投資ラウンドに参加し、11社の企業を対象として、1億3200万米ドルを提供することを発表した。Intel Capitalは、「今回の投資ラウンドでは、AI(人工知能)技術や自律計算、IC設計などの分野に注力している」と述べている。 PCIeの進化が支える次世代インターコネクト技術

PCIeの進化が支える次世代インターコネクト技術

高速バスインタフェース「PCI Express 4.0(PCIe Gen4)」がまさに今、プロセッサ市場に登場しようとしている。しかし、多くの企業は既に、「PCIe 5.0(PCIe Gen5)」が数年以内に登場すると見込んでいるようだ。さらに、「PCIe Gen6」の開発も同時に進められているという。 ハード開発をよりオープンに、団体設立が相次ぐ

ハード開発をよりオープンに、団体設立が相次ぐ

IntelとRISC-Vの支持者たちがそれぞれ、ライバル同士となるアライアンスの設立を発表した。未来のプロセッサを見据え、競合するエコシステムを構築していくという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待