大規模集積量子コンピュータ向けに集積構造を考案:ラビ振動は従来比約10倍高速に

産業技術総合研究所(産総研)は、シリコンスピン量子ビット素子を用いた大規模集積量子コンピュータ向けの新しい集積構造を考案した。従来構造に比べ、ラビ振動(スピンの操作速度)が約10倍高速となり、製造ばらつき耐性も大幅に改善できるという。

製造ばらつき耐性を改善、100万個程度の量子ビットが集積可能に

産業技術総合研究所(産総研)デバイス技術研究部門新原理デバイス研究グループの飯塚将太産総研特別研究員と森貴洋主任研究員らは2021年8月、シリコンスピン量子ビット素子を用いた大規模集積量子コンピュータ向けの新しい集積構造を考案したと発表した。従来構造に比べ、ラビ振動(スピンの操作速度)が約10倍高速になり、製造ばらつき耐性も大幅に改善できるという。

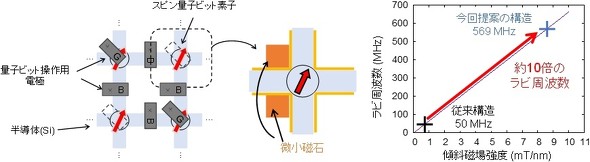

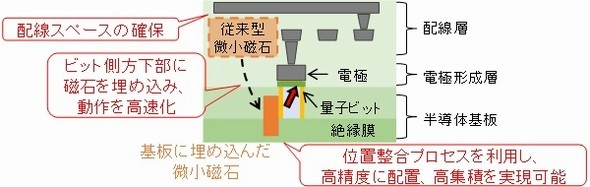

産総研は今回、スピン量子ビット素子の高速動作に必要な微小磁石を集積する新たな構造を開発した。これまで素子上部にあった微小磁石を、素子の側方下部に形成する構造である。

これによって、微小磁石がスピン量子ビット素子に近づき、より強い傾斜磁場を得ることができるようになった。しかも、素子上部に配線スペースを確保することができるため、高い製造ばらつき耐性が得られる「自己整合型プロセス技術」を用いることが可能になった。

開発した構造は、格子状のビット配置を想定した。シリコンスピン量子ビット素子の性能を評価するデバイスシミュレーターの計算結果により、スピン量子ビット素子の四隅のうち、2カ所に微小磁石を配置した時が、最も強い傾斜磁場強度になることが分かった。ラビ周波数は569MHzになり、従来構造の50MHzに比べて約10倍も高くなることを確認した。

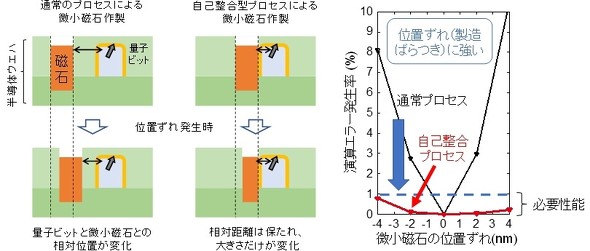

開発した構造の製造ばらつき耐性もシミュレーターによって検証した。今回、自己整合型プロセス技術を採用したことで、スピン量子ビット素子と微小磁石の相対ずれがなくなり、製造ばらつきによる特性不良が発生しにくくなることが分かった。

この特長について、演算エラー発生率を用いて検証した。特性不良の判定値は、演算エラー発生率1%に設定した。開発した構造を採用したことで、スピン量子ビットと微小磁石の位置が4nmずれても、演算エラー発生率は1%以下となる。従来構造ではわずか1nmのずれでも許容できないレベルだという。

製造プロセスで用いられる最先端の極端紫外線リソグラフィ装置で発生する位置ずれは、不良発生率の指標である3σ値が2nm程度とされている。これに対し、開発した構造はその2倍となる4nm(6σ値)までのずれが許容できるという。6σ値を超える不良発生率は100万個に3個となり、製造ばらつき耐性は100万個程度まで集積可能な水準であることが分かった。従来構造では10個程度の集積が限界であったという。

産総研は、開発したスピン量子ビット素子特性を模擬できるデバイスシミュレーション技術を生かし、大規模集積量子コンピュータの実現に向けた技術開発や検証を、引き続き進める計画である。量子回路の設計や大規模な極低温実験評価技術の実用化にも取り組む考えだ。

関連記事

産総研、MRAMの磁気安定性を飛躍的に改善

産総研、MRAMの磁気安定性を飛躍的に改善

産業技術総合研究所(産総研)は、原子層レベルで制御されたタンタル(Ta)を下地に用いることで、磁気抵抗メモリ(MRAM)の磁気安定性を飛躍的に改善する技術を開発した。 透明電極の結晶化抑えた透明有機デバイスを開発

透明電極の結晶化抑えた透明有機デバイスを開発

産業技術総合研究所(産総研)は、透明酸化物電極(透明電極)を有する有機デバイスにおいて、透明電極の結晶化を抑制することで、性能が大幅に向上することを発見した。この成果はこれまでの予想に反する結果だという。 産総研、超伝導量子アニーリングマシンを開発

産総研、超伝導量子アニーリングマシンを開発

産業技術総合研究所(産総研)は、超伝導量子アニーリングマシンの開発と動作実証に成功した。従来方式に比べ1桁少ない量子ビット数で、組み合わせ最適化問題を解くことが可能になるという。 量子センサーのスピン情報、電気的読み出しに成功

量子センサーのスピン情報、電気的読み出しに成功

東京工業大学と産業技術総合研究所(産総研)の共同研究グループは、ダイヤモンド量子センサーのスピン情報を、電気的に読み出すことに成功した。感度が高い集積固体量子センサーの実現が期待される。 産総研、空気中の湿度変化で発電する電池を開発

産総研、空気中の湿度変化で発電する電池を開発

産業技術総合研究所(産総研)は、空気中の湿度変化を利用して発電する「湿度変動電池」を開発した。溶液からなる素子のため内部抵抗が極めて小さく、mAレベルの電流を連続して取り出すことに成功した。 MRAM用単結晶MTJ素子を300mmウエハー上に作製

MRAM用単結晶MTJ素子を300mmウエハー上に作製

産業技術総合研究所(産総研)は、MRAM用の単結晶MTJ(磁気トンネル接合)素子をシリコンLSIに集積化するための3次元積層プロセス技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

今回考案した新しいシリコンスピン量子ビット素子と微小磁石の集積構造を模した図 出典:産総研

今回考案した新しいシリコンスピン量子ビット素子と微小磁石の集積構造を模した図 出典:産総研