「CoWoS」の標準アーキテクチャが顧客による開発期間を短縮:福田昭のデバイス通信(336) TSMCが開発してきた最先端パッケージング技術(9)(2/2 ページ)

広帯域メモリ「HBM」とSoCを混載する「CoWoS_S」の構成とレイアウトを標準化

「CoWoS_S」の主流は、広帯域メモリモジュール「HBM(High Bandwidth Memory)」と大規模なSoCを混載した高性能サブシステムである。Siインターポーザを介してHBMとSoCを接続することで、広帯域のメモリアクセスを実現する。

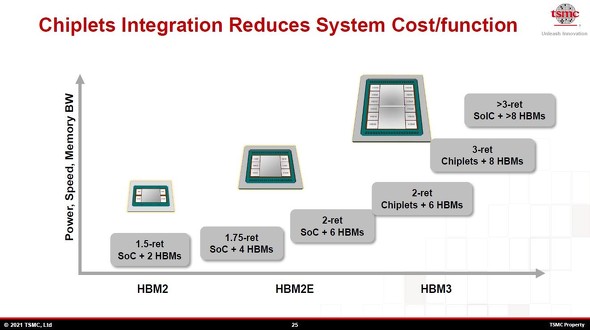

「HBM」の仕様は世代ごとに共通規格が定められている。製品への普及は第2世代の「HBM2」から始まった。次の世代はHBM2の強化版「HBM2E」である。さらに次の世代は「HBM3」で、大容量化と広帯域化が進む。加えて「CoWoS_S」に搭載するHBMの数量は増加し、Siインターポーザの面積は拡大し、SoCの製造技術は微細化する。SoCはシングルダイからチップレット、さらにはSoIC(System on Integrated Chips)へと形態を変える。「CoWoS_S」を構成する要素技術は増加し、かつ複雑になる。

広帯域メモリモジュール「HBM」の進化(横軸)と、対応する「CoWoS_S」の消費電力、速度、メモリ帯域の推移(縦軸)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

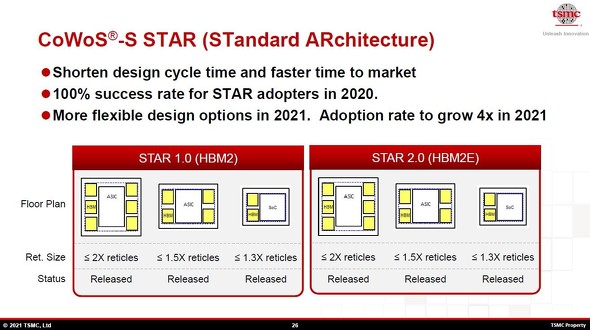

広帯域メモリモジュール「HBM」の進化(横軸)と、対応する「CoWoS_S」の消費電力、速度、メモリ帯域の推移(縦軸)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)そこでTSMCは、顧客である半導体ベンダーが「CoWoS_S」を採用したサブシステムを素早く開発できるように、構成とレイアウトを標準化した「CoWoS_S STAR(STandard ARchitecture)」を提供している。HBM2に対応する「STAR 1.0」と、HBM2Eに対応する「STAR 2.0」を用意した。

SoCとHBMを混載する「CoWoS_S」の構成を標準化した「CoWoS_S STAR」の概要[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

SoCとHBMを混載する「CoWoS_S」の構成を標準化した「CoWoS_S STAR」の概要[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)標準化しているのはSiインターポーザの最大寸法とHBMの個数、それからシリコンダイのレイアウトなどである。最大構成と中間の構成、最小構成の3つの基本仕様を顧客は選べる。

最大構成は、レチクルの2倍に相当する露光面積のSiインターポーザを最大寸法とする。SoC(あるいはASIC)を中央にレイアウトし、その左右に3個ずつのHBMを配置する。中間の構成はレチクルの1.5倍に相当する露光面積をSiインターポーザの最大寸法とする。SoCは中央にレイアウトし、その左右に2個ずつのHBMを配置する。最小構成はレチクルの1.3倍に相当する露光面積をSiインターポーザの最大寸法とする。SoC(あるいはASIC)の側面に沿って2個のHBMを配置している。

最大構成から最小構成までの標準仕様は、HBM2対応の「STAR 1.0」とHBM2E対応の「STAR 2.0」で変わらない。「STAR 1.0」の開発資産を「STAR 2.0」で再利用することを意識しているように見える。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

TSMCが語る「N3」ノードの詳細

TSMCが語る「N3」ノードの詳細

TSMCは現在、「N5」プロセスノード適用製品の生産を順調に拡大しているところだが、それをさらに進化させた「N4」ノードの量産を2021年中に開始する予定だと発表した。また、N4よりもさらなる技術的飛躍を実現するとみられる「N3」ノードについても、2022年後半には量産を開始する計画だという。 ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 多層配線のビア抵抗を大幅に低減する「スーパービア」

多層配線のビア抵抗を大幅に低減する「スーパービア」

今回は、奇数番号(あるいは偶数番号)で隣接する配線層(2層上あるいは2層下の配線層)を接続するビア電極の抵抗を大幅に下げる技術、「スーパービア(supervia)」について解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待