AMDが開発した第4世代のZenコア「Zen4」の概要:福田昭のデバイス通信(373)(2/2 ページ)

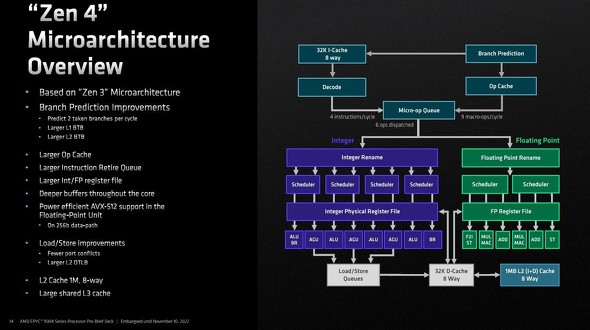

「Zen3」に数多くの改良を加えた「Zen4」のマイクロアーキテクチャ

「Zen4」のマイクロアーキテクチャは、前世代の「Zen3」をベースに数多くの改良を加えた。分岐予測の強化(サイクル当たりに2つの分岐を予測、分岐先バッファ(BTB)の拡大)、マイクロOpキャッシュ(内部命令キャッシュ)の増量、命令リタイアキューの拡大、整数レジスタファイルと浮動小数点レジスタファイルの拡張、AVX-512命令セットのサポート、ロード/ストアの改良、2次キャッシュの拡大、などがある。

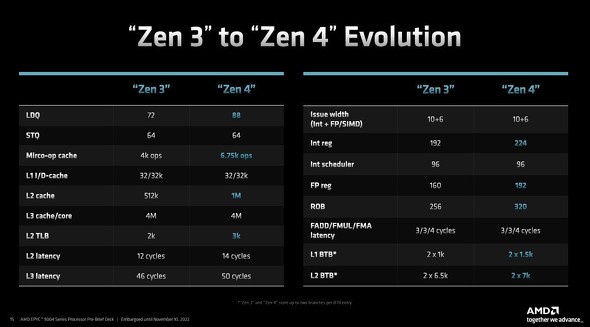

「Zen3」と「Zen4」の比較。Zen4では、ロードキュー(LDQ)のエントリ数を増やす、マイクロOpキャッシュが格納可能な命令数を増やす、2次(L2)キャッシュ容量を2倍に拡大、2次TLBのエントリ数を1.5倍に増加、整数レジスタファイルと浮動小数点レジスタファイルの増量、ROB(リオーダーバッファ)の増加、1次BTBと2次BTBの拡大などの改良がみられる[クリックで拡大] 出所:AMD

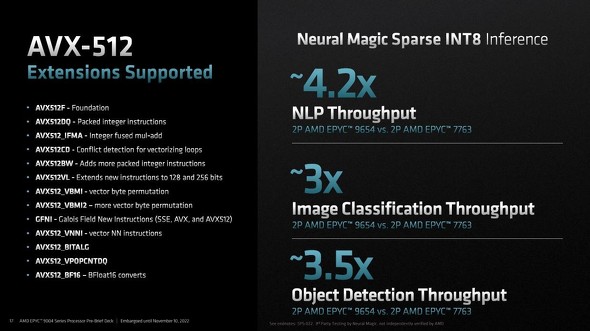

「Zen3」と「Zen4」の比較。Zen4では、ロードキュー(LDQ)のエントリ数を増やす、マイクロOpキャッシュが格納可能な命令数を増やす、2次(L2)キャッシュ容量を2倍に拡大、2次TLBのエントリ数を1.5倍に増加、整数レジスタファイルと浮動小数点レジスタファイルの増量、ROB(リオーダーバッファ)の増加、1次BTBと2次BTBの拡大などの改良がみられる[クリックで拡大] 出所:AMD特筆すべきは浮動小数点演算で256ビット幅のAVX-512拡張命令をサポートしたことだろう。AVX-512には数多くの命令セットがあり、Zen4ではVNNI(Vector Neural Network Instruction)命令やBFloat16命令といった機械学習の処理を高速化する命令をサポートする。

その結果、Zen3コアのプロセッサ(64コア構成のEPYC)に比べ、Zen4のプロセッサ(96コア構成のEPYC)は自然言語処理のスループットが約4.2倍、画像分類処理のスループットが約3倍、物体検出処理のスループットが約3.5倍と大きく向上したという。

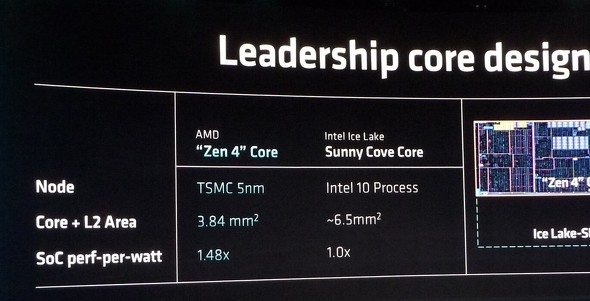

5nmのFinFETプロセスでTSMCが製造

前回で述べたように、第4世代のEPYCプロセッサである「EPYC 9004」シリーズは8個のCPUコアを内蔵したミニダイ(チップレット)を入出力ミニダイとともに基板に搭載した。CPUコアを内蔵するミニダイ(CCD)は、Zen4コアとコアごとの2次キャッシュ、共有3次キャッシュ、入出力ダイとのインタフェース回路で構成される。製造技術は5nmのFinFETプロセス。製造担当企業はTSMCである。

AMDは新製品発表会「together we advance_data centers」で、Zen4コアと2次キャッシュを含めたシリコンの面積を3.84mm2としていた。8個のコアを搭載するので、単純計算では30.72mm2となる。これに32Mバイトの共有3次キャッシュとインタフェース回路を加えると、1枚のCCDが出来上がる。

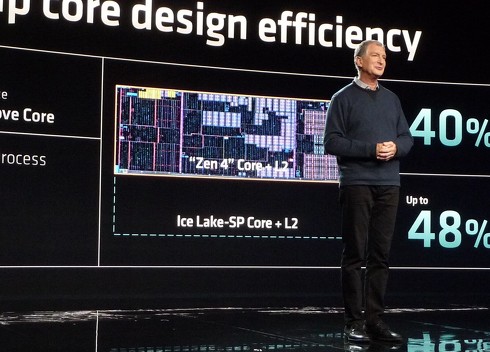

CPUコアと2次キャッシュを含めたシリコンの面積。Zen4と、Intelの10nmプロセスによるCPUコア(Sunny Cove)を比較した。2022年11月10日(米国時間)にAMDが開催した新製品発表会「together we advance_data centers」の講演を筆者が撮影したもの[クリックで拡大]

CPUコアと2次キャッシュを含めたシリコンの面積。Zen4と、Intelの10nmプロセスによるCPUコア(Sunny Cove)を比較した。2022年11月10日(米国時間)にAMDが開催した新製品発表会「together we advance_data centers」の講演を筆者が撮影したもの[クリックで拡大] Zen4コアと2次キャッシュを含めたシリコンの回路レイアウト。2022年11月10日(米国時間)にAMDが開催した新製品発表会「together we advance_data centers」の講演を筆者が撮影したもの。中央はAMDのCTO兼EVP(テクノロジーおよびエンジニアリング担当)をつとめるMark Papermaster氏[クリックで拡大]

Zen4コアと2次キャッシュを含めたシリコンの回路レイアウト。2022年11月10日(米国時間)にAMDが開催した新製品発表会「together we advance_data centers」の講演を筆者が撮影したもの。中央はAMDのCTO兼EVP(テクノロジーおよびエンジニアリング担当)をつとめるMark Papermaster氏[クリックで拡大]⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。 HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

米Western Digitalの「2023会計年度第1四半期」(2022年7月〜9月)を紹介する。 携帯型MP3プレーヤーの黎明期(1997年〜1998年)

携帯型MP3プレーヤーの黎明期(1997年〜1998年)

今回はフラッシュメモリを記憶媒体とする携帯型デジタルオーディオプレーヤー(DAP:Digital Audio Player)を扱う。時期は1997年〜1998年である。 ワイヤレス電力伝送で実際に電子機器を動作させる

ワイヤレス電力伝送で実際に電子機器を動作させる

今回は「7.4 試作例」の講演パートを解説する。ワイヤレス受電端末を試作し、低消費電力の小型機器をワイヤレス電力伝送で動かした。 ワイヤレス受電用端末の試作に向けたアンテナの設計作業

ワイヤレス受電用端末の試作に向けたアンテナの設計作業

今回は「7.2 アンテナ」と「7.3 アンテナの集積化」の内容について、簡単に解説する。 ワイヤレス電力伝送の過去から未来までを展望

ワイヤレス電力伝送の過去から未来までを展望

今回から、「IEDM 2021」でオランダimec Holst Centreでシニアリサーチャー、オランダEindhoven University of TechnologyでフルプロフェッサーをつとめるHubregt J. Visser氏が講演した「Practical Implementation of Wireless Power Transfer(ワイヤレス電力伝送の実用的な実装)」の内容を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長