AIチップ/RISC-Vプロセッサの新興企業、日本に本格進出:CEOはJim Keller氏(2/2 ページ)

RISC-Vプロセッサでは8-wideの高性能版を開発

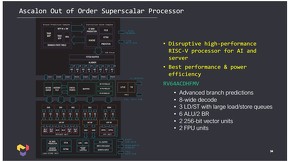

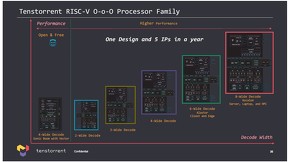

RISC-Vプロセッサについては、Tenstorrentは「Ascalon」というプロセッサを既に設計している。2023年末にはAscalonの試作品を発表できる見込みだという。Ascalonは、アウトオブオーダー実行を行うプロセッサで、命令デコード幅は8-wide。256ビットのベクトルユニットと、FPU(Floating Point Unit)をそれぞれ2基搭載するという高い性能を持つことが特長だ。Ascalonは、HPC(High Performance Computing)やサーバなどエンタープライズ向けの設計になっているが、命令デコード幅を2-wide、3-wide、4-wide、6-wideにシュリンクしたバージョンもそろえる。「消費電力や用途に応じて使い分けられるようになっている」(中野氏)。さらに、Ascalonを複数組み合わせたクラスターを構成することもできる。

左=「Ascalon」のアーキテクチャ/右=RISC-Vプロセッサの設計IPでは、命令デコード幅が異なる5種類(図中では色の付いた枠で囲んでいる)を用意している[クリックで拡大] 出所:Tenstorrent

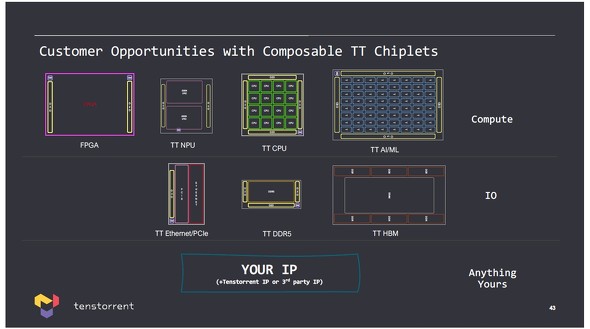

左=「Ascalon」のアーキテクチャ/右=RISC-Vプロセッサの設計IPでは、命令デコード幅が異なる5種類(図中では色の付いた枠で囲んでいる)を用意している[クリックで拡大] 出所:TenstorrentTenstorrentのAIアクセラレーターやRISC-Vプロセッサの他、他社のFPGAやメモリなどを組み合わせ、チップレットのIPとして提供することもできる。「チップレットでは、テープアウトまでサポートする」(中野氏)

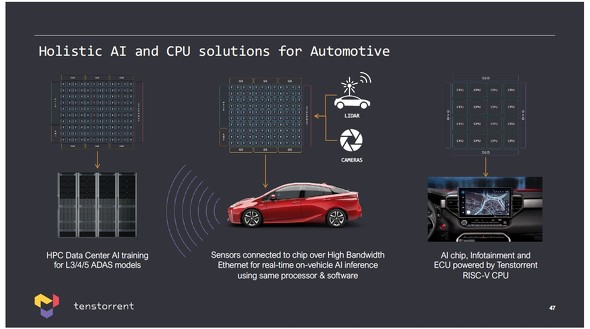

Tenstorrentのターゲットの一つが自動車だ。中野氏は一例として、車内でリアルタイムに推論を行うADASや、車載インフォテインメントを挙げた。「当社のIPを使うことで、プロセッサの開発期間を大幅に短縮できる他、チップレットによって機能を容易にチューニングできるようになる。小規模から大規模まで同一アーキテクチャで対応できるので、開発ノウハウの流用や開発工数の削減にも貢献する」(中野氏)。Tenstorrentは車載アプリケーションに向けて、評価用ボードやマシンも提供している。

関連記事

“天才設計者”Jim Keller氏がAI新興企業のCTOに

“天才設計者”Jim Keller氏がAI新興企業のCTOに

著名なチップ設計者アーキテクトのJim Keller氏が、カナダのAI(人工知能)チップ新興企業Tenstorrentに社長兼CTO(最高技術責任者)として入社した。Tenstorrentの取締役会にも加わる予定だ。Keller氏は、過去にAMD、Intel、Tesla、Appleなどに勤務したことがあり、長いキャリアの中で多くの実績を残している。 プロセッサ市場の下剋上なるか? Intelを追うAMDを躍進させた2人の立役者

プロセッサ市場の下剋上なるか? Intelを追うAMDを躍進させた2人の立役者

プロセッサ市場では、ある異変が起きている。Intelが長年トップに君臨しているこの市場で、AMDがシェアを急速に拡大しているのだ。今回は、AMDの躍進の背景にいる2人の立役者に焦点を当てよう。 クラウドAI特化のチップで手応え、超高知能AI開発も

クラウドAI特化のチップで手応え、超高知能AI開発も

2016年に設立された英スタートアップのGraphcoreは、データセンター/クラウドでの機械学習に特化したプロセッサIPU(Intelligence Processing Unit)の開発を手掛ける企業だ。同社のIPUは金融、医療、自動車、消費者向けインターネットサービスなど、さまざまな分野で導入されている。Graphcoreの共同設立者兼CEO(最高経営責任者)のNigel Toon氏に、Graphcoreのビジネスの現状や、次世代IPU、日本での戦略について聞いた。 「RISC-Vは不可避の存在」、RISC-V Summit 2022詳報

「RISC-Vは不可避の存在」、RISC-V Summit 2022詳報

RISC-V ISAの管理/推進を目指すコンソーシアム「RISC-V International」が2022年12月に開催した「RISC-V Summit 2022」について、当日行われた講演の内容や各社の最新開発動向などを紹介する。 RISC-Vコア、「出荷コア数で2024年には主流へ」

RISC-Vコア、「出荷コア数で2024年には主流へ」

米国SiFiveは、RISC-Vの現状やSiFiveにおける今後の取り組みなどを紹介した。この中で、「RISC-Vの立ち上がりは早く、2024年にはRISC-Vの出荷コア数がArmを上回り、逆転するのではないか」との見通しを明らかにした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増