裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023:湯之上隆のナノフォーカス(64)(2/7 ページ)

Workshops、Short Courses、本会議の参加者数

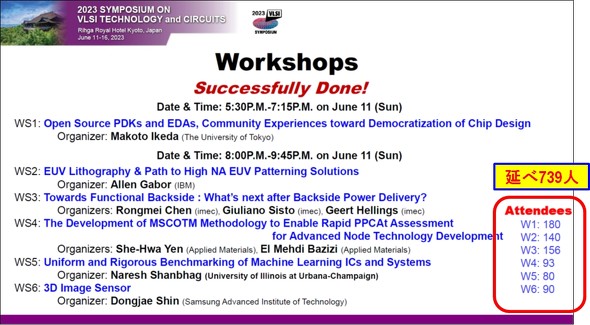

VLSI2023の前夜祭的な位置付けとして、6月11日(日)の夜に、6件のWorkshopsが行われた(図4)。Workshopsは、本会議では取り上げにくいテーマにフォーカスすることを目的として、2019年に試験的に導入された。

拙著記事「半導体業界のトレンドは「3次元化」が明確に VLSI 2019」によれば、初年度の2019年のWorkshopsでは、Atomic Layer Processing(83人)、2D Materials(47人)、3D Integration(61人)の3つのテーマで合計191人が参加した。

ところがその4年後のVLSI2023では、「本会議では取り上げにくいテーマ」だけでなく、Backside Power Deliveryなど、現在の旬のテーマも加えられており、その延べ参加人数は739人にのぼっている。この参加者数をみると、もはやWorkshopsは、本会議の前座とは言えないのではないか?

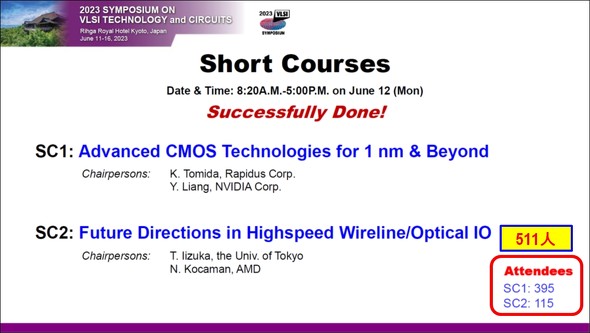

次に、6月12日(月)に行われたShort Courses(SC)を見てみよう(図5)。SCでは、2つのセッションが同時開催された。SC1は“Advanced CMOS technologies for 1 nm & beyond”(395人)、SC2は “Future directions in Highspeed Wireline/Optical IO”(115人)で、合計511人が参加した(ただし、この511人はリアルに参加した人数であり、参加登録した人数は689人に上っている)。

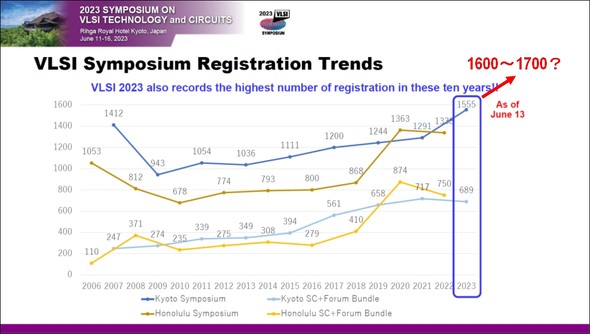

そして本会議では、6月13日に集計した時点で1555人がレジストレーションを行っている(図6)。この人数は、過去10年間で最多であるが、6月13日以降に登録する人もいるだろうし、6月19日以降のオンデマンドで参加する人もいるだろう。となると、VLSI2023の参加者は、恐らく1600人を超え、もしかしたら1700人に迫る人数になるのではないか。

前述した通り、多くの発表会場では立ち見が出るほど満席で、2カ所のバンケット会場は入りきれないほどの人出だった。もし今後も参加者数が増え続けた場合、リーガロイヤルホテル京都のキャパシティーでは対応できないように思う。

それでは、異常と思えるほどの論文数と参加者数を記録したVLSI2023で、筆者はどの発表に注目したか。最初にその概要を述べると以下の通りである。

1)GAA構造が注目される先端ロジック半導体では、裏面電源供給ネットワーク(Backside Power Delivery Network: BSPDN)がブレークする予感を覚えた

2)DRAMでは、14nmノード付近からEUVが使われているが、2020年代後半に“3D DRAM”が登場する可能性がある

3)積層数の増大が続いている3D NANDでは、新たなドライエッチング技術の登場により、今後もより一層、積層数が増大していくだろう

では、まず、先端ロジック半導体の注目発表を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増