0.2Vでデータ保持できる新型CMOSメモリ技術を開発、東京科学大:待機時電力は不揮発メモリ並みに

東京科学大学の菅原聡准教授らによる研究グループは、0.2Vという極めて低い電圧でデータを保持できるCMOSメモリ技術を開発した。試作したSRAMマクロは、待機時の電力を不揮発性メモリ並みに削減できるという。

伝達特性のヒステリシス幅を最大化できる新型インバーターを提案

東京科学大学総合研究院未来産業技術研究所の菅原聡准教授、塩津勇作研究員、同大学工学院電気電子系の伊藤克俊大学院生(当時)による研究グループは2025年10月、0.2Vという極めて低い電圧でデータを保持できるCMOSメモリ技術を開発したと発表した。試作したSRAMマクロは、待機時の電力を不揮発性メモリ並みに削減できるという。

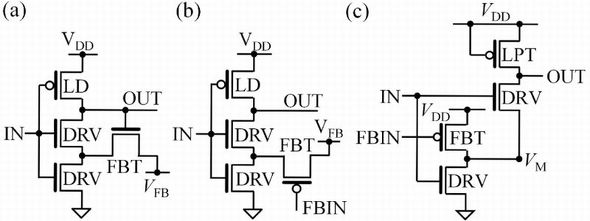

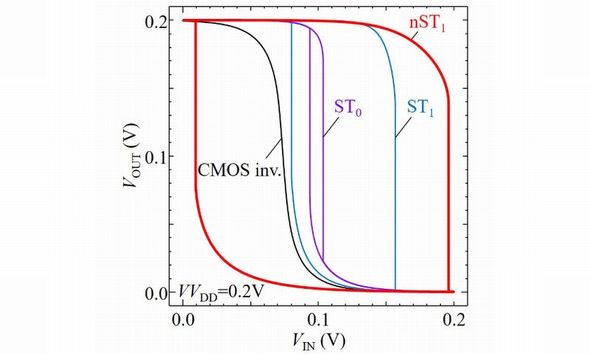

研究グループはこれまで、極めて低い電圧でデータを保持できるSRAM(ULVR-SRAM)の研究に取り組んできた。そして、伝達特性(VTC)のヒステリシス幅を最大化できる新型インバーター(nST1)を提案した。

このnST1インバーターは、シュミットトリガー(ST1)インバーターにおける入力段のpMOSを入力から切り離し、入力段インバーターを疑似nMOS構成にしたものに相当するという。つまり、nST1インバーターはこのpMOSによるリーク電流によって駆動される。実験結果から、nST1インバーターは、0.2VにおいてVTCのヒステリシス幅は最大化されていることが分かった。

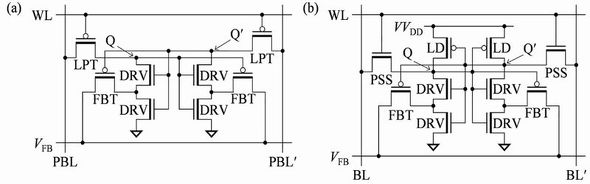

次に、nST1インバーターを用い新型のULVR-SRAMを開発した。従来のSRAMにおけるロードトランジスタ(LD)とパストランジスタ(PSS)を1つのトランジスタ(LPT)に統合できるため、少ないトランジスタ数でセルを構成できるという。今回は8トランジスタ(8TU)でSRAMセルを構成し、セル構造の最適化を行った。

最適化したセルについて、モンテカルロシミュレーションにより不良率解析を行った。動作電圧が0.2V、動作温度が25℃および85℃の条件で、8TUセル、10TUセルおよび、6TセルのULVRモードにおける疑似スタティックノイズマージン(QSNM)の分散を比べた。

この結果、8TUセルのQSNM分布は、他のセルに比べ高い電圧側に位置し、ノイズ耐性は最も強いことが分かった。特に、6σ不良率における8TUセルのQSNMは、10TUセルの2倍となった。動作電圧が0.16Vでも、8TUセルは極めて低い不良率を示した。

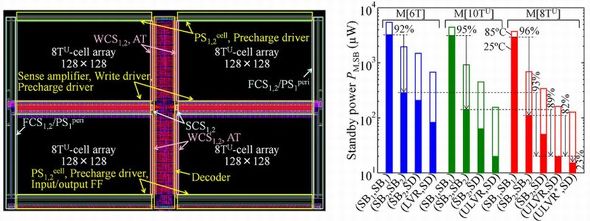

研究グループは、8TUセルを用い8kバイトのULVR-SRAMマクロ(M[8TU])を開発した。性能を比較するため、6Tセルや10TUセルを用いたマクロも設計し、待機時の電力を調べた。

開発したM[8TU]は、「スタンバイ(クロック有)」「スタンバイ(クロックゲーティング)」「超低電圧リテンション」「電源遮断」という、いずれの動作モードにおいても待機時の電力が小さかった。特に、動作モードがULVRの場合、従来セルを用いたSRAMマクロに比べ、待機時電力を93%も削減できることが分かった。0.16VのULVRモードでは、0.2VのULVRに比べ待機時電力をさらに23%削減できるという。

関連記事

乾電池1本分の電圧で発光する深青色有機ELを開発、東京科学大

乾電池1本分の電圧で発光する深青色有機ELを開発、東京科学大

東京科学大学総合研究院フロンティア材料研究所の研究チームは、乾電池1本分の電圧(1.5V)で光る深青色有機ELの開発に成功した。次世代ディスプレイ規格に近い青色発光を低電圧で行うことが可能となる。 室温で紫〜橙色に光るp型/n型半導体を実現、東京科学大

室温で紫〜橙色に光るp型/n型半導体を実現、東京科学大

東京科学大の研究チームは、考案した独自の設計指針に基づき、p型/n型半導体特性や光学特性を広範囲に制御できる材料を開発した。開発したスピネル型硫化物は、高効率の緑色LEDや太陽電池に向けた新材料として有用であることを実証した。 人工光触媒をパネル化、CO2からギ酸を大量生成へ

人工光触媒をパネル化、CO2からギ酸を大量生成へ

三菱電機と東京科学大学は、可視光を吸収するポリマー状の窒化炭素(PCN)を固定化した光触媒パネルを用い、CO2からギ酸を生成することに成功した。ギ酸の大量生成を可能にすることで、再生可能エネルギーの利用拡大に貢献していく。 乾電池1本分の電圧で発光する白色有機ELを開発

乾電池1本分の電圧で発光する白色有機ELを開発

東京科学大学と大阪大学の研究チームは、乾電池1本分の電圧で発光する白色有機ELを開発した。青色のアップコンバージョン有機EL(UC-OLED)技術を応用しつつ、発光素子内に水色と黄色の発光色素を加えることにより、低電圧駆動で白色化を実現した。 Naイオン電池向け正極材料のポテンシャルを「富岳」で解明

Naイオン電池向け正極材料のポテンシャルを「富岳」で解明

東京科学大学や早稲田大学らの研究グループは、Naイオン電池の正極材料として注目されている多孔性結晶「プルシアンブルー(PB)」におけるNaイオンの拡散機構を解明し、その全貌を明らかにした。高精度な原子レベルの第一原理分子動力学計算(FPMD)にはスーパーコンピュータ「富岳」を活用した。 京大やトヨタなど、全固体フッ化物イオン二次電池用正極材料を開発

京大やトヨタなど、全固体フッ化物イオン二次電池用正極材料を開発

京都大学らの研究グループは、量子科学技術研究開発機構や東京大学、兵庫県立大学、東京科学大学および、トヨタ自動車らと共同で、全固体フッ化物イオン二次電池用の高容量インターカレーション正極材料を新たに開発した。ペロブスカイト酸フッ化物が、既存のリチウムイオン二次電池正極材料に比べ2倍を超える可逆容量を示すことが分かった。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増