GAA構造トランジスタの試作が国内で可能に、産総研が試験ライン構築:国内装置メーカー3社との共同研究がベース

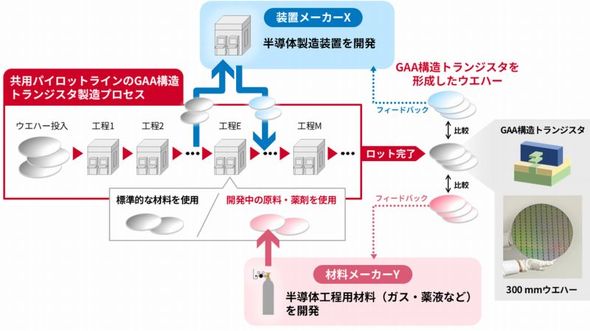

産業技術総合研究所(産総研)先端半導体研究センターは、国内半導体製造装置メーカー3社と共同研究した成果に基づき、GAA構造のトランジスタを、300mmシリコンウエハー上に試作し、技術の検証などを行うことができる国内唯一の「共用パイロットライン」を構築した。

最先端トランジスタの試作や技術検証、動作確認が国内で可能に

産業技術総合研究所(産総研)先端半導体研究センターは2025年11月、国内半導体製造装置メーカー3社と共同研究した成果に基づき、GAA(Gate All Around)構造のトランジスタを300mmシリコンウエハー上に試作し、技術の検証などができる国内唯一の「共用パイロットライン」を構築したと発表した。

最先端ロジック半導体向けトランジスタの構造はFin型から、多段の極薄膜シリコンチャネルをゲートで包むGAA構造への移行が進む。こうした立体構造を持つトランジスタを製造する工程は一段と複雑となり、高度なプロセス技術が求められている。ただ、最新のトランジスタを試作しても国内にはそれを検証/評価できる施設がなく、これまでは海外機関に頼らざるを得なかったという。

産総研先端半導体研究センターは今回、NEDOの助成事業である「ポスト5G情報通信システム基盤強化研究開発事業」における「先端半導体の前工程技術(More Moore技術)の開発」(2021〜2025年度、実施機関は東京エレクトロン、SCREENセミコンダクターソリューションズ、キヤノン)に対応した共同研究として、「先端3次元構造ロジック半導体デバイスの構造・プロセス技術の開発と検証用パイロットライン整備」に取り組んできた。

この中で、産総研スーパークリーンルームの300mmパイロットラインへ、産総研仕様に対応した最先端半導体製造装置を新たに16台導入し、GAA構造のトランジスタを試作できる共用パイロットラインを構築した。

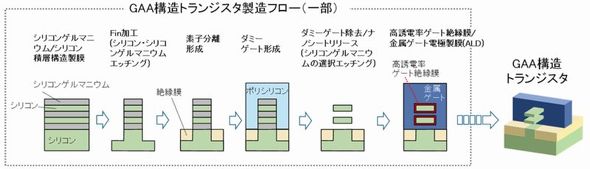

これを実現するために必要となる要素プロセスも新たに開発した。「多段シリコンナノシートを形成するシリコン・シリコンゲルマニウム結晶膜成膜技術」「シリコンナノシート層のみを残してシリコンゲルマニウム層を選択エッチングする技術」「シリコンナノシートを囲むゲート絶縁膜とゲート金属電極を堆積させる成膜技術」「トランジスタのしきい値を制御するためのゲート絶縁膜厚と金属膜厚を精密に調整する原子層堆積(ALD)技術」などだ。

これらの要素プロセスは、東京エレクトロンやSCREENセミコンダクターソリューションズ、キヤノンらと個別に連携して開発した。これらのプロセスは、プロセスモジュールとして活用できるように整備し、全てのプロセスは産総研がそのノウハウを管理するという。パイロットラインは国内の企業や大学などに提供される。このため、利用者は最先端トランジスタの試作から技術の検証、動作の確認までを国内で実施できる。ようになる。

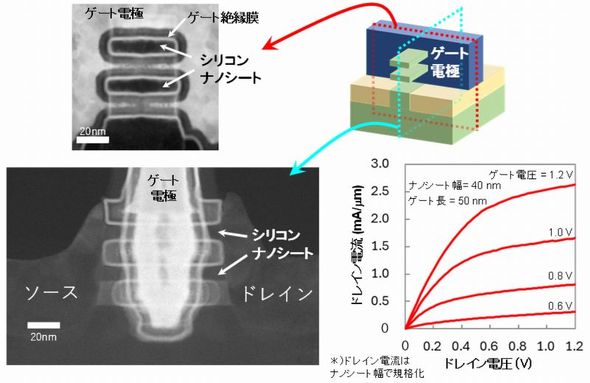

実験では、ゲート電極の断面電子顕微鏡画像によって、シリコンナノシートの周りをゲート絶縁膜とゲート電極が取り囲んでいる形状を確認した。また、ソース・チャネル・ドレインを横切る断面電子顕微鏡画像によって、シリコンナノシートがソース・ドレイン電極に正しく接続されていることが分かった。電気特性を評価したところ、ゲート電圧を印加するとドレイン電流がオンオフ制御される正常な電流電圧特性が得られていることも確認できた。

今後は、「ゲート電極の微細化」や「nチャネル型トランジスタとpチャネル型トランジスタによるCMOS化」「要素プロセスの高度化と拡充」などに取り組み、トランジスタの性能や信頼性の向上、低消費電力化などを可能にする技術を開発していくことにしている。

関連記事

名古屋大ら、溶液成長法による6インチp型SiCウエハー試作に成功

名古屋大ら、溶液成長法による6インチp型SiCウエハー試作に成功

オキサイドパワークリスタルとMipox、UJ-Crystal、アイクリスタル、産業技術総合研究所(産総研)および名古屋大学の開発グループが、溶液成長法とシミュレーション技術を活用し、6インチp型炭化ケイ素(SiC)ウエハーおよび、6インチ/8インチn型SiCウエハーの試作に成功した。 太陽光パネルのカバーガラスから希少元素を回収

太陽光パネルのカバーガラスから希少元素を回収

産業技術総合研究所(産総研)は、太陽光パネルで用いられたカバーガラスの中から、希少元素「アンチモン(Sb)」を効率よく分離し回収するための技術を、中部電力と共同で開発した。今回は「水熱処理技術」を用い、廃ガラスの中から約8割のSbを抽出することに成功した。 電力損失を半減した鉄系磁性材料を開発 EV応用に期待

電力損失を半減した鉄系磁性材料を開発 EV応用に期待

物質・材料研究機構(NIMS)は、東北大学や産業技術総合研究所(産総研)と共同で、電力損失を従来の半分以下に抑えることができる鉄系磁性材料を開発した。高周波トランスや電気自動車(EV)の駆動用電源回路といった用途での採用が期待される。 「内部が空洞」のマイクロバンプで低温接合、新たな半導体実装技術

「内部が空洞」のマイクロバンプで低温接合、新たな半導体実装技術

東北大学の研究グループは産業技術総合研究所(産総研)と共同で、表面活性化接合とテンプレートストリッピングの技術を組み合わせて、中空ピラミッド構造のマイクロバンプを作製し、異種材料を低温で強固に接合できる半導体実装技術を開発した。 急速充放電特性に優れる「分子イオン電池」開発へ

急速充放電特性に優れる「分子イオン電池」開発へ

産業技術総合研究所(産総研)は、大阪公立大学工業高等専門学校や愛媛大学と共同で、電荷担体に分子イオンを用いる「分子イオン電池」が、急速充放電特性に優れていることを実証した。 Ge半導体で「電気が流れやすくなる」方法を開発

Ge半導体で「電気が流れやすくなる」方法を開発

産業技術総合研究所(産総研)と東北大学は、電極材料にテルル化ビスマス(Bi2Te3)を用い、この薄膜とn型Geを反応させることで、電子が流れやすい界面を形成することに成功した。エネルギー障壁をこれまでの約半分に低減できるという。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増