AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール:2026年から順次リリース

Rapidusは2025年12月17日、同社2nm製造プロセス向けの半導体設計支援ツール群「Raads」を発表した。2026年から順次リリース予定で、設計期間の50%短縮と、設計コストの30%削減が可能だとしている。

エージェントAIで設計期間50%短縮、コスト30%削減

Rapidusは2025年12月17日、「SEMICON Japan」(東京ビッグサイト)でメディア向けのブリーフィングを開催し、半導体設計支援ツール群「Raads」を発表した。2026年度から順次提供を開始する。

Rapidusは、半導体の設計支援から前工程、後工程までを一貫して手掛ける「RUMS(Rapid and Unified Manufacturing Service)」構想を掲げている。その一環として、複雑化する先端半導体の設計ハードルを下げるべく、AIを活用した設計支援ツール「Raads(Rapidus AI-Assisted Design Solution)」を開発してきた。

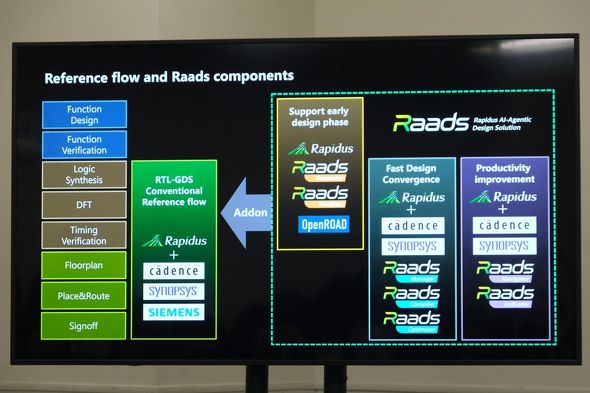

AIの性能が向上し、簡単な論理設計もできるようになってきたことから、Raadsを「Rapidus AI-Agentic Design Solution」へとレベルアップさせ、Rapidusの半導体開発製造拠点「IIM-1」(北海道千歳市)での2nm製造プロセス向けの設計支援ツールとして具現化した。全6個のツールを提供予定で、全て活用すれば、設計期間を50%短縮し、設計コストを30%削減できるとする。

Rapidusの最高技術責任者(CTO)を務める石丸一成氏は「Rapidusは設立以来、他ファウンドリーとの差別化の手段として、スピードをターゲットの1つにしている。今回のRaadsなどを活用して、世界最短のTAT(Turn Around Time)を目指す」としている。

LLMベースのEDAやデバッグツールを展開

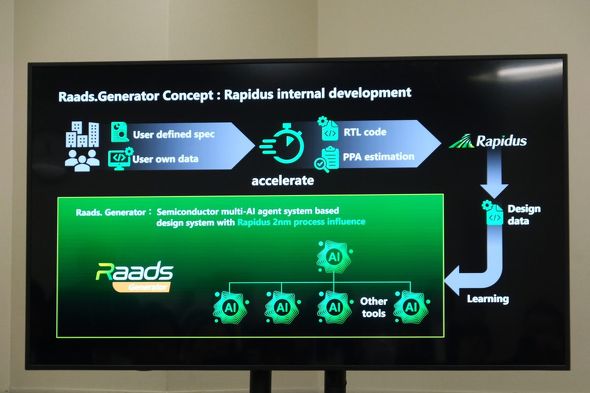

ブリーフィングでは一部ツールの紹介も実施。「Raads Generator」は大規模言語モデル(LLM)ベースのEDAツールで、自然言語で半導体の仕様を入力すると、Rapidusの2nm製造プロセスに最適化されたRTL(Register Transfer Level)設計データを出力する。

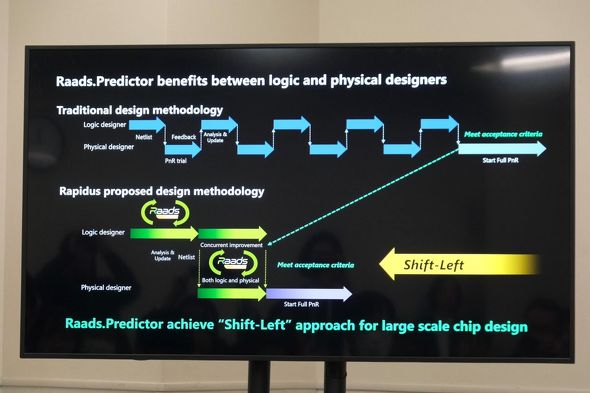

「Raads Predicor」はデバッグや物理設計、配置配線の最適化が可能なツール。通常の半導体設計では、論理設計者と物理設計者が細かくやりとりし、事前に予想される物理的な課題を解決した状態で物理設計に移行する。本ツールを使えば、論理設計者だけで物理課題を解決できるため、より早く物理設計に移行できるという。

このほか、LLMで設計者をアシストする「Raads Navigator」「Raads Indicator」、機械学習(ML)、AIを活用した階層レイアウト設計ツール「Raads Manager」、ML、AIでPPA(Power Performance Area)を最適化するためのパラメータを導出できる「Raads Optimizer」のリリースを予定する。

Raads Generator、Raads Predicorの2個はオープンソースで、Rapidusでの2nm製造を検討する顧客には無償提供を予定。他ツールはライセンス品として、有償で提供予定だという。

関連記事

Rapidusは31年度に上場目指す、27年度後半に2nm世代量産

Rapidusは31年度に上場目指す、27年度後半に2nm世代量産

赤沢亮正経済産業大臣は2025年11月21日、政府がRapidusに対して1000億円を出資する考えを発表した。また、この日公開されたRapidusの実施計画では、同社が2031年度頃に株式上場を目指す方針などが明らかになった。 ついにできた!Rapidus試作ライン稼働、2nm GAAトランジスタの動作を確認

ついにできた!Rapidus試作ライン稼働、2nm GAAトランジスタの動作を確認

Rapidusは、最先端半導体の開発/生産を行う「IIM-1」(北海道千歳市)で、2nm GAA(Gate All Around)トランジスタの試作を開始し、動作を確認したと発表した。Rapidus 社長兼CEOの小池淳義氏は「2nm GAAトランジスタがこのスピードで本当にできたということに、顧客は非常に驚き、ものすごい期待を持つだろう」と語った。 2nm半導体設計基盤でRapidusとシーメンスが協業

2nm半導体設計基盤でRapidusとシーメンスが協業

Rapidusは、2nm世代以降の半導体設計・製造プロセスに関し、シーメンスデジタルインダストリーズソフトウェア(以下、シーメンス)と戦略的協業を行うことで合意した。シーメンスが提供する設計/検証ツール「Calibreプラットフォーム」をベースにPDK(プロセスデザインキット)を共同開発し、設計・検証のエコシステムを構築していく。 Rapidus、試作は25年7月以降 性能に自信も「楽観できない」

Rapidus、試作は25年7月以降 性能に自信も「楽観できない」

Rapidusは、2025年度の新エネルギー・産業技術総合開発機構(NEDO)の研究開発事業の計画/予算承認を受けた。これを受け、2nmパイロットラインの立ち上げを開始する。 Rapidusが2nm GAAウエハーの試作品を展示 「特需」に期待の北海道

Rapidusが2nm GAAウエハーの試作品を展示 「特需」に期待の北海道

2025年4月のパイロットライン稼働に向けて業界内で注目度が高まる中、我が地元も盛り上がっています。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増