サムスンとSK Hynix、ISSCCで次世代メモリを披露:メモリ/ストレージ技術

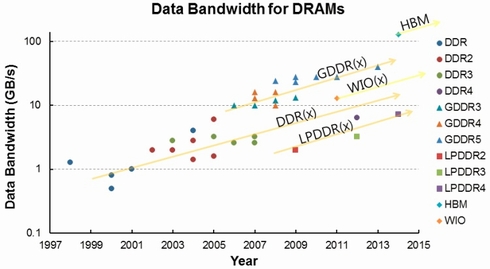

Samsung Electronics(サムスン電子)とSK Hynixは、2014年に開催される半導体集積回路技術の国際会議「ISSCC 2014」で、LPDDR4や広帯域メモリ(HBM)など、次世代のメモリを披露する。

Samsung ElectronicsとSK Hynixは、2014年2月に米国カリフォルニア州サンフランシスコで開催される「ISSCC(IEEE International Solid-State Circuits Conference) 2014」でそれぞれリポートを発表し、ローエンドとハイエンドのメモリチップの未来について説明するようだ。

Samsungは、低消費電力のスマートフォン向けLPDDR4を公開する。電圧1.0V、端子当たりの帯域幅は3.2Gビット/秒だという。同チップは25nmプロセスを用いて製造される。

ISSCCの主催者によると、これらのチップは、これまでに発表された中で最も速い転送速度と最も高い密度を実現しているという。2014年内には、既存のLPDDR3チップの代替メモリとして、スマートフォンなどへの導入が始まるとみられている。

LPDDR4メモリとは別に、Samsungは、0.064mm2のSRAMセルを発表する予定だ。同SRAMセルは、14nm世代のFinFETプロセスで製造されるという。

SK Hynixは広帯域メモリ(HBM: High-Bandwidth Memory)を初公開する。8Gビットのこのメモリは、シリコン貫通電極(TSV)を使って4個のダイを積層したもので、29nmプロセスを用いて製造されている。電圧は1.2V、メモリ帯域幅は128Gバイト/秒を実現する。8チャンネルをサポートし、1024本のI/Oを備える。

ライバルであるMicron Technologyは、HBMに似た「Hybrid Memory Cube(HMC)」と呼ばれるメモリスタックの開発計画を打ち出している。HMCは、通信、グラフィックス、サーバといった分野に向けるという。Micronは既に、HMCのサンプル出荷を開始している。容量は4Gバイト、メモリ帯域幅は160Gバイト/秒だ。

【翻訳:青山麻由子、編集:EE Times Japan】

関連キーワード

Samsung | DDR4 | ISSCC | LPDDR | DRAM | Hybrid Memory Cube | SRAM | メモリ/ストレージ技術(エレクトロニクス) | Micron

関連記事

次世代メモリ「HMC」の仕様バージョン1を公開

次世代メモリ「HMC」の仕様バージョン1を公開

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。 サムスン電子が「業界初」の3次元NANDを量産

サムスン電子が「業界初」の3次元NANDを量産

Samsung Electronics(サムスン電子)は、メモリセルを垂直に積層した3次元セル構造のNAND型フラッシュメモリの量産を発表した。記憶容量は128Gビットで、セルの積層数を増やすなどすれば、将来的には1テラビット容量も可能だという。 サムスン電子、DDR4メモリの量産を開始

サムスン電子、DDR4メモリの量産を開始

Samsung Electronics(サムスン電子)は、4GビットDRAMをベースにしたDDR4メモリモジュールの量産を開始した。20nmのプロセスを適用していて、2.667Gビット/秒の転送速度を実現している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増