ルネサス、16nm FinFETを用いたSRAMを開発:新技術

ルネサス エレクトロニクスは2014年12月、16nmプロセス世代以降の車載情報機器用SoC(System on Chip)向け回路技術を開発したと発表した。

ルネサス エレクトロニクスは2014年12月16日、16nmプロセス世代以降の車載情報機器用SoC(System on Chip)向け回路技術を開発し、同技術を用いて16nmプロセスSRAMを作成し、0.7Vの低電圧動作条件で641p(ピコ)秒の高速読み出しを実現したと発表した。

16nmプロセスは、これまでのプレーナー型MOSFETよりも、消費電力の抑制や性能向上が図りやすいフィン構造を導入した新しいFinFETが用いられる。ただ、「FinFETでは、回路定数の最適化を行うことが困難であり、新たな設計回路技術の開発が課題だった」(ルネサス)。そこで、ルネサスは今回、FinFET用に低電圧でも安定して高速読出し/書込み動作が可能となる、新しい回路技術を開発。この回路技術を採用したSRAMを16nmプロセス FinFETで試作し、0.7Vの低電圧動作条件にて、641p秒の高速動作を確認したとする。

開発した回路技術の概要は次の通り。

低電圧下で高速読出し/書込みを両立するワード線オーバードライブ方式回路技術

半導体プロセスの微細化とともにデバイス素子のばらつきが増大することで、デバイスの下限動作電圧が悪化する傾向があり、その対策として回路的に工夫する回路技術(以下、アシスト回路)が導入されている。従来は、読出し動作時の安定動作を確保するため、アクセス時にワード線の電圧をわずかに下げる工夫をしていた。しかし、この方式では、書込み時の動作マージンの悪化や、読出し速度が著しく低下するなどの課題があった。

これに対し、ルネサスは、FinFETの特徴を生かし、これまでとは逆にワード線電圧をわずかに昇圧し、読出し時と書込み時でそのパルス幅を変えるというアシスト回路方式を採用。これにより、読出し時と書込み時の動作マージンを確保しつつ、高速な読出し動作を実現した。

FinFET固有のばらつきを考慮した高信頼、最適設計

FinFETでは、これまでのプレーナー型MOSFETとは異なる素子ばらつきがある。アレイ状に並んだメモリセルの中央部と端部で、読出し動作時にビット線に流れる電流にオフセットが生じることにより電流差が発生する。そのため、読出し時のセンスアンプマージンが確保できず、デバイスが誤動作する可能性があり、この電流差を十分に考慮したマージン設計を行う必要がある。

ルネサスでは、この電流オフセットを試作したテストチップで実測することで定量的に確認。その上で、この実測結果から最適な動作マージンを確保できるように回路の微調整を行うことが可能にした。

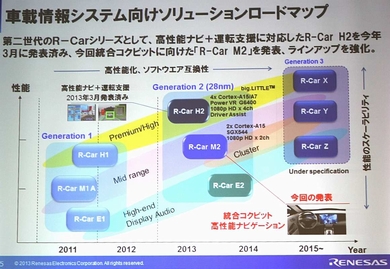

2015年発表予定の「R-Car」に搭載へ

ルネサスでは、開発したアシスト回路技術について、「今後プロセスの微細化が進むにつれて困難になると予想される速度と安定動作の両立を実現しており、将来の先進運転支援システムや自動運転に求められるリアルタイム画像処理の性能向上に大きく貢献できる。今回開発したSRAMを16nm FinFETプロセスのルネサスの最先端SoCに採用し、いち早く提供する」としている。なお、同社は、2015年にも発表する予定の車載情報機器向けSoC「R-Car」の第3世代品に、16nmプロセスを採用する方針を2014年11月の「electronica 2014」などで表明している(関連記事:ルネサスの車載情報機器向けSoC、第3世代「R-Car」は16nmプロセス、最大8コアに)。

関連記事

ルネサスの車載情報機器向けSoC、第3世代「R-Car」は16nmプロセス、最大8コアに

ルネサスの車載情報機器向けSoC、第3世代「R-Car」は16nmプロセス、最大8コアに

ルネサス エレクトロニクスはドイツ ミュンヘンで開催中の「electronica 2014」(2014年11月11〜14日)で、車載情報機器向けSoC「R-Car」など車載向け半導体の展示を行うとともに、次世代の「第3世代R-Car」製品に16nmプロセスを採用し、最大8つのCPUコアを搭載する方針を明かした。 ルネサス、統合コックピット向けソリューションでカーナビ用SoC「シェア75%維持目指す」

ルネサス、統合コックピット向けソリューションでカーナビ用SoC「シェア75%維持目指す」

ルネサス エレクトロニクスは車載情報機器向けSoC「R-Car」の第2世代シリーズのミッドレンジ向け製品「R-Car M2」を発表した。同SoCは、パートナーとの連携を図りながら、ソフトウェアやツール類と組み合わせた提案を行い拡販する方針。現状、「ナビゲーション向けSoCで世界シェア75%」(同社)というポジションの維持を狙う。 FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。 TSMC、16nm FinFETのリスク生産を開始

TSMC、16nm FinFETのリスク生産を開始

TSMCが16nmプロセスを適用したFinFETのリスク生産を開始した。開発スケジュールは予定よりも早く進んでいるようだ。今後は、AppleやQualcommなどが、新しい世代のFinFETの製造を、TSMCとSamsung Electronicsのどちらにどの程度発注していくのかが注目される。 Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsung Electronics(サムスン電子)が、ARM主催のイベントで14nm世代のFinFETプロセス技術を適用したチップを発表した。TSMCもその直前に16nm FinFETプロセスを用いたARM「Cortex-A57」の検証を行っているが、ある専門家は、16/14nm FinFETの性能については、SamsungとTSMCは互角だとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か