有線通信編:40Gビット/秒の超高速伝送を実現する回路技術:徹底プレビュー「ISSCC2015の歩き方」(7)(2/2 ページ)

消費電力を低減した10Gビット/秒のシリアルリンク

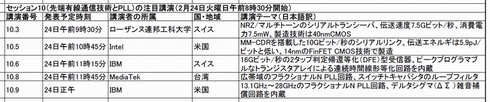

セッション10(先端有線通信技術とPLL)では、消費電力を下げた有線通信回路の研究開発成果が数多く発表される。

スイスのローザンヌ連邦工科大学(EPFL)とスイスの半導体開発企業Kandou Busは共同で、7.5mWと消費電力が低く、7.5Gビット/秒を伝送するシリアルデータ・トランシーバを発表する(講演番号10.3)。マルチドロップのメモリ・インタフェース向けである。製造技術は40nmのCMOS。

米国のIntelは、1ビット当たりのデータ転送エネルギーが5.9pJと低いシリアルリンクの開発成果を公表する(講演番号10.5)。データ転送速度は10Gビット/秒。MM-CDR(Mueller-Muller baud-rate Clock Data Recovery)機能を備える。製造技術は14nmのFinFET CMOS技術である。

スイスのIBMは、2タップの判定帰還等化器(DFE)を備えた、16Gビット/秒対応でGビット/秒当たりの消費電力が2mWと低い受信器を発表する(講演番号10.6)。プログラマブルなアクティブピーキング・トランジスタアレイを有する連続時間線形等化器(CTLE)を内蔵する。

このほか、フラクショナルN PLL回路の開発成果を台湾MediaTek(講演番号10.8)と米国IBM(講演番号10.9)がそれぞれ発表する。

25Gビット/秒のシリコン光リンク技術

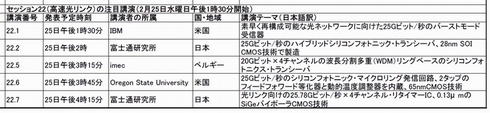

セッション22(高速光リンク)では、電子回路と光回路を融合したシリコンフォトニクス技術による高速トランシーバの講演が相次ぐ。

富士通研究所や富士通などの共同研究グループは、ハイブリッドシリコンフォトニクス技術による25Gビット/秒のトランシーバを発表する(講演番号22.2)。製造技術は28nmのSOI CMOS技術である。富士通研究所は、光リンク向けのリタイマーICの開発成果も公表する(講演番号22.7)。25.78Gビット×4チャンネル出力である。製造技術は130nmのシリコンゲルマニウム(SiGe)・バイポーラCMOS技術。

ベルギーのimecを中心とする研究チームは、波長分割多重(WDM)リングをベースとするシリコンフォトニクス技術で実現した20Gビット/秒×4チャンネル(合計で80Gビット/秒)のトランシーバを報告する(講演番号22.5)。

米国のOregon State Universityを中心とする研究チームは、シリコンフォトニクス技術による25Gビット/秒のトランスミッタ(送信器)を発表する(講演番号22.6)。2タップの非対称フィードフォワード等化器(FFE)と動的温度調整器を搭載した。製造技術は65nmのCMOS技術である。

関連記事

量子通信の実現へ、量子もつれ光の高速生成技術を開発

量子通信の実現へ、量子もつれ光の高速生成技術を開発

情報通信研究機構(NICT)は2014年12月、電気通信大学と共同で、光ファイバー通信波長帯における量子もつれ光子対の生成効率を30倍以上に高める技術を開発した。 400Gビット級光伝送技術の実用化にめど、NTTなど3社が開発

400Gビット級光伝送技術の実用化にめど、NTTなど3社が開発

NTTとNEC、富士通の3社は、チャネル当たり毎秒400Gビット級の光伝送技術の実用化にめどをつけた。開発した技術を光送受信装置に実装すれば、既存の光ファイバを活用して、従来に比べて4倍の光伝送を実現することが可能となる。 「量子通信の実現に大きな突破口」、NICTが中継増幅技術を開発

「量子通信の実現に大きな突破口」、NICTが中継増幅技術を開発

情報通信研究機構(NICT)などは、量子通信を長距離化する新しい「中継増幅技術」の実証に成功したと発表した。NICTは「量子暗号の長距離化や量子通信の実現に大きな突破口を与えるもの」としている。 8K非圧縮映像の長距離伝送、NICTなどが実験に成功

8K非圧縮映像の長距離伝送、NICTなどが実験に成功

情報通信研究機構などは、研究開発用のテストベッドネットワーク「JGN-X」上で、さっぽろ雪まつりで収録された8K(7680×4320画素)非圧縮映像の長距離伝送(東京〜大阪間)に成功した。同社は「100Gビット/秒のネットワークを利用した8K非圧縮映像の長距離伝送は世界で初めて」と主張する。 テレビ映像を「元からきれいにする」には

テレビ映像を「元からきれいにする」には

テレビ放送では、映像が幾つもの中継地点を経由することが多い。従来の手法では映像が中継されるごとに色が劣化していた。富士通が開発したアルゴリズムを利用すると、色の劣化が起きなくなり、テレビの画質を元からきれいにできる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長