ARMから見た7nm CMOS時代のCPU設計(14)〜次々世代の異次元トランジスタ:福田昭のデバイス通信(25)(2/2 ページ)

半導体FETの究極は垂直方向のナノワイヤ

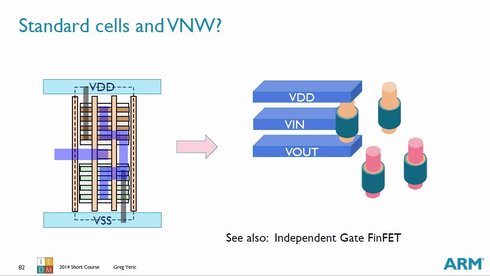

シリコン面積当たりのトランジスタ数(トランジスタ密度)をHNW構造よりも高めるには、円筒状のチャンネルをシリコンウエハー表面と垂直な方向に配置する。この構造は「バーチカルナノワイヤ(VNW)」と呼ばれる。VNW構造は、既存の半導体材料を前提としたときは、究極のトランジスタ密度を得られる構造といえる。

実は、VNW構造に類似のトランジスタは既に量産が始まっている。最先端NANDフラッシュメモリが採用したメモリセル構造「3D NAND」である。細長い円筒状のチャンネルに32個から48個ものセルトランジスタを作り込んだ構造であり、製造がきわめて難しい。現在のところ、チャンネルのピッチは40nm近くあるので、ナノワイヤと呼べるほどチャンネルは細くない。だが近い将来、ナノワイヤ・レベルの微細な加工を必要とする段階へと移行する可能性は低くない。

ただし、メモリとロジックでは根本的に異なる点がある。それはレイアウト設計だ。メモリセルアレイはマトリクス配置なので、VNW構造でも比較的容易に配置配線の設計を実行できる。これに対して数多くのスタンダードセルを用意するロジックでは、VNW構造を前提としたスタンダードセルは、どのような構造になるのかが未知数である。考えるのは早過ぎる課題かもしれないが、VNW構造のFETを実用化するときにスタンダードセル設計が避けて通れない課題であることも、確かなのである。

7nm世代以降のトランジスタは混沌(こんとん)の状態

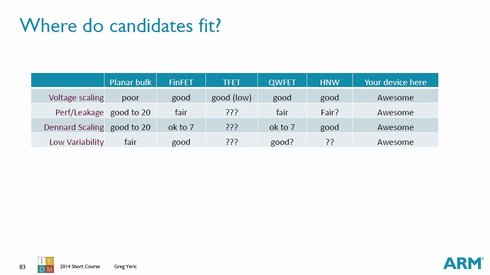

ARMは講演で、従来から次世代、次々世代に至るトランジスタを一覧表でまとめて示した。一覧表の左端が従来のトランジスタ(プレーナのバルク)、右端が次々世代のトランジスタ候補となっており、おおむね、左から右へと時間が進んでいる。

既存技術であるプレーナ・バルク・トランジスタは電圧スケーリングが限界に来ている。性能とリーク電流が良好でいられるのは20nm世代まで、スケーリング則がかろうじて成り立つのも20nm世代までである。

最新技術であるFinFETは電圧スケーリングがまだ可能で、7nm世代までは行けそうだとの見解である。代替候補のトンネルFET(TFET)はまだ、未知数の部分が多い。QWFET(量子井戸)FETはFinFETと同様の見込みがありそうだ。HNW(ホリゾンタルナノワイヤ)は電圧スケーリングと微細化は可能だが、リーク電流やばらつきなどは未知数である。

(次回に続く)

関連記事

トランジスタも捨てたものではない

トランジスタも捨てたものではない

さまざまな機能の回路がIC化されて流通している現在、個別素子のトランジスタを使う機会は少ないという方もいるかもしれない。しかしトランジスタは応用範囲が広く、使いこなせばとても便利だ。今回は、通常はオペアンプICやコンパレータICを使って構成する回路を、わずか3個のトランジスタで作る方法を紹介しよう。 量子情報処理の実用化に道筋、東大が室温で単一光子発生に成功

量子情報処理の実用化に道筋、東大が室温で単一光子発生に成功

東京大学 ナノ量子情報エレクトロニクス研究機構の荒川泰彦教授らは、位置制御されたGaN(窒化ガリウム)系ナノワイヤ量子ドットを用いて、300K(27℃)の室温で単一光子の発生に成功した。今回の開発成果は、量子暗号通信や量子コンピュータなど、量子情報処理システムの実用化に向けた研究に弾みをつける可能性が高い。 「微細化は今後10年続く」――インテルの見解

「微細化は今後10年続く」――インテルの見解

米国で開催された「IEDM(International Electron Devices Meeting)2014」。Intelの14nm FinFETプロセスやTSMCの16nm FinFETなどの開発状況をはじめ、多くの論文が発表された。IEDM 2014のリポートを数回にわたってお届けする。 「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

BroadcomのCTO(最高技術責任者)が、「ムーアの法則はあと15年ほどで終えんを迎える。半導体プロセスの微細化は、5nm以降はほぼ進歩しない」という見解を示した。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増