EE Times Japan >

プロセス技術 >

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(imec編):福田昭のデバイス通信(90)(2/2 ページ)

» 2016年09月27日 09時30分 公開

[福田昭,EE Times Japan]

ロジックの微細化とその課題

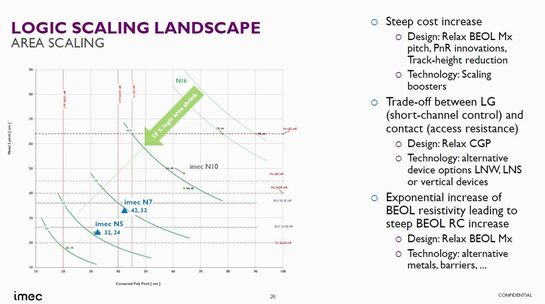

Lauwers氏はまた、CMOSロジックを微細化していくときの定量的な数値をグラフで示すとともに、微細化の課題を列挙した。

グラフの縦軸は第2層金属配線のピッチ(標準的なプロセスだとこの配線層が最も密になる、M2ピッチ)、グラフの横軸はコンタクトの多結晶シリコン配線ピッチ(コンタクトピッチ)である。現行世代(N世代)の16/14nmノードだと、例えばコンタクトピッチが78nm、M2ピッチが64nmとなる(曲線なので両者は相反関係にある)。

N+1世代(10nm世代)では、例えばコンタクトピッチが64nm、M2ピッチが48nmとなる。そしてN+2世代(7nm世代)では例えばコンタクトピッチが42nm、M2ピッチが32nm、N+3世代(5nm世代)では例えばコンタクトピッチが32nm、M2ピッチが24nmと短くなっていく。

このような微細化を進めていくときの課題は少なくない。レイアウト設計では、バックエンドの金属配線ピッチを詰めすぎないこと、配置配線技術に革新が求められること、トラックの高さを抑えることといった課題がある。デバイス設計では、ゲート長(短チャンネル効果)とコンタクトピッチ(コンタクト抵抗)のトレードオフが厳しくなる。バックエンドの設計では、配線による抵抗増大と容量増大が激しくなる。銅配線に換わる材料の探索が必要になるかもしれない。

(次回に続く)

⇒「福田昭のデバイス通信」バックナンバー一覧

関連記事

GFの7nm FinFETプロセス、2018年にも製造開始へ

GFの7nm FinFETプロセス、2018年にも製造開始へ

GLOBALFOUNDRIES(GF)が、7nm FinFETプロセスの開発計画を発表した。2018年後半には同プロセスでの製造を開始する予定だという。さらに、同じく2018年には、22nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスで製造するチップにおいて、ギガビット未満の低容量の混載MRAM(磁気抵抗メモリ)をサポートする予定だ。 「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(JSR Micro編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(JSR Micro編)

大手レジストベンダーJSR Microの講演では、主に同社とimecの共同開発の内容が発表された。その1つが、JSR MicroのEUV(極端紫外線)レジストをimec所有のEUV露光装置で評価するというもので、化学増幅型のEUVレジストによってハーフピッチ13nmの平行直線パターンを解像できたという。さらに、5nm世代のEUVリソグラフィの目標仕様と現状も紹介された。 2020年、5nm世代でEUV時代が到来か

2020年、5nm世代でEUV時代が到来か

ASMLは2016年4〜6月にEUV(極端紫外線)リソグラフィ装置を4台受注し、2017年には12台を販売する計画を明かした。これを受けて業界では、EUV装置によるチップ量産が、5nmプロセス世代での製造が見込まれる2020年に「始まるかも」との期待感が広がっている。 半導体業界、次なる買収ターゲットは?

半導体業界、次なる買収ターゲットは?

半導体業界におけるM&Aの嵐は収まる気配がない。2016年も、2015年ほどの数ではないものの、大規模な買収が相次いでいる。では、現時点で買収のターゲットとなりそうな“残っている企業”はどこなのだろうか。 新型TMR素子、室温環境でMR比92%を達成

新型TMR素子、室温環境でMR比92%を達成

産業技術総合研究所の齋藤秀和企画主幹は、全単結晶トンネル磁気抵抗(TMR)素子を開発した。TMR素子の磁気抵抗変化率(MR比)は室温環境で92%と極めて大きい。待機電力ゼロのコンピュータを実現できる技術として期待される。 産総研、ナノ炭素材料の新しい合成法を開発

産総研、ナノ炭素材料の新しい合成法を開発

産業技術総合研究所の徐強上級主任研究員らは、棒状やリボン状に形状制御されたナノ炭素材料の新しい合成法を開発した。キャパシターの電極材料への応用などが期待されるナノ炭素材料を、高い収率で量産することが可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR