ISSCC技術講演の最終日午前ハイライト(その1)、バラつきに強いオンチップ電源と高速低消費のLDOレギュレーター:福田昭のデバイス通信(132) 2月開催予定のISSCC 2018をプレビュー(8)(2/2 ページ)

低消費で高速のデジタルLDOレギュレーター技術が続出

このセッションで他に目立つのは、抵抗と電流による電圧降下(IRドロップ)や応答速度などを改善した低損失型リニアレギュレーター(LDO(low-dropout)レギュレーター)の発表である。5件の発表が予定されている。

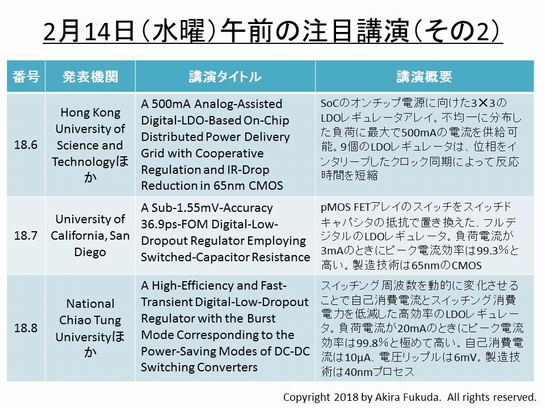

具体的には、中国マカオのUniversity of Macau他の共同研究グループ(講演番号18.4)、University of MinnesotaとCisco Systemsの共同研究チーム(講演番号18.5)、中国香港のHong Kong University of Science and TechnologyとシンガポールQualcommの共同研究チーム(講演番号18.6)、University of California, San Diego(講演番号18.7)、台湾National Chiao Tung Universityと台湾Realtek Semiconductorの共同研究チーム(講演番号18.8)がそれぞれ、開発成果を報告する。

University of Macau他の共同研究グループは、自己消費電流が430nAと低いLDOレギュレーター回路を発表する(講演番号18.4)。負荷変動に対するコンダクタンスを高めた、NANDゲートによるアナログアシスト回路を開発した。nMOSFETをパワートランジスタに採用している。出力電流が20mAのときにドロップアウト電圧は最小50mVと低い。製造技術は28nmのCMOS、シリコン面積は0.0055mm2である。

University of MinnesotaとCisco Systemsの共同研究チームは、応答速度と自己消費電力のトレードオフをうまくバランスさせたLDOレギュレーター回路を開発した(講演番号18.5)。ビート周波数の量子化回路によって標本化周波数を制御する。標本化周波数を固定した回路に比べ、セトリング時間を25分の1に、電圧ドループを5分の1に縮めた。製造技術は65nm、シリコン面積は0.0374mm2である。

Hong Kong University of Science and Technology(HKUST)とQualcommの共同研究チームは、SoC(System on a Chipのオンチップ電源に向けた3×3のアナログアシストLDOレギュレーターアレイを報告する(講演番号18.6)。不均一に分布した負荷に最大で500mAの電流を供給可能。9個のLDOレギュレーターは、位相をインタリーブしたクロック同期によって応答時間を短縮。製造プロセスは65nmのCMOSである。

University of California, San Diegoは、pMOSFETアレイのスイッチをスイッチドキャパシターの抵抗で置き換えた、フルデジタルのLDOレギュレーターを発表する(講演番号18.7)。負荷電流が3mAのときにピーク電流効率は99.3%と高い。定常状態の電圧リップルは1.5mV未満。製造技術は65nmのCMOSである。

National Chiao Tung UniversityとRealtek Semiconductorの共同研究チームは、スイッチング周波数を動的に変化させることで自己消費電流とスイッチング消費電力を低減した高効率のLDOレギュレーターを報告する(講演番号18.8)。負荷電流が20mAのときにピーク電流効率は99.8%と極めて高い。自己消費電流は10μA、電圧リップルは6mVである。負荷電流が1mAから20mAに変化したときの電圧ドループは40mV(応答時間は1.3μS)。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ISSCC(国際固体回路会議)とは何か

ISSCC(国際固体回路会議)とは何か

毎年2月に開催される、半導体チップの回路技術とシステム技術に関する国際学会「ISSCC(国際固体回路会議)」。えり抜きの論文が発表される重要なイベントだ。今回から始まる本シリーズでは、開催を2カ月後に控えたISSCCについて、概要と注目論文を紹介する。 “ハイブリッド構成”の降圧DC-DCコントローラー

“ハイブリッド構成”の降圧DC-DCコントローラー

Analog Devices(ADI)は、入力電圧範囲が10〜72VのDC-DCコントローラー「LTC7821」を発表した。スイッチドキャパシター回路と同期整流式降圧DC-DCコントローラー回路を組み合わせ、1チップにした製品で、従来に比べて実装面積を最大50%低減できる。 優れたアナログ技術が、高度なIoT社会を支える

優れたアナログ技術が、高度なIoT社会を支える

高度なIoT(モノのインターネット)社会を実現するために欠かせないのが、優れたアナログ技術である。「アナログ・グル」と呼ばれるアナログ回路技術者が、難しい課題を解決するための技術などについて語った。 半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

2008〜2017年まで主に米国で開催されてきた「国際メモリワークショップ(IMW)」が、2018年は日本の京都で開催される。今回はIMWの概要を紹介しよう。 反強誘電体キャパシターから不揮発性メモリを作る方法

反強誘電体キャパシターから不揮発性メモリを作る方法

二酸化ハフニウムは、条件次第で「反強誘電体(Antiferroelectrics)」になるが、反強誘電体の薄膜にある工夫を加えると、不揮発性メモリに応用可能になる。その「工夫」とは何だろうか。 わずか0.1mm単位の攻防が生んだiPhone X

わずか0.1mm単位の攻防が生んだiPhone X

Appleが、「iPhone」誕生10周年を記念して発売した「iPhone X」。分解すると、半導体技術のすさまじい進化と、わずか0.1mmオーダーで設計の“せめぎ合い”があったことが伺える。まさに、モバイル機器がけん引した“半導体の10年の進化”を体現するようなスマートフォンだったのだ――。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング