Lam Researchが打ち立てた金字塔、“1年間メンテナンスフリー”のドライエッチング装置:湯之上隆のナノフォーカス(31)(6/6 ページ)

3次元NANDのメモリホールへの適用

以上のように、Lamはチャンバ内部に設置したリングでプラズマを物理的に閉じ込めた絶縁膜ドライエッチング装置により、強制的なダミーランは不要となり、常にクリーンなチャンバで安定したエッチング速度を実現し、同一チャンバでエッチングとアッシングの連続処理ができるようになった。

このような特徴を持つLamの絶縁膜ドライエッチング装置が、3次元NANDのメモリホールの開口に必要不可欠な装置となった。その理由は以下の通りである。

まず、従来の装置で、1枚のウエハー当たり1時間かかるメモリホールを開口することを考えてみよう。図8に示したように、最初に行わなければならないのは、強制的にダミーランを行って反応生成物をチャンバ内に付着させることである。1枚1時間だから2〜3枚程度、ダミーランを行うことになるだろう。次に、本番のエッチングに進むわけだが、1枚1時間のエッチングで何枚のウエハーが着工できるだろうか?

2016〜2017年頃、筆者が聞いていた話では、1ロット(25枚)も持たない模様だった。すると、従来装置では、毎日、チャンバを大気開放して、”チャンクリ“を行わなければならなかったということになる。この生産性の低さでは、とても3次元NANDの大量生産には使えない。

一方、Lamの装置では、どのようになるだろうか。まず、ダミーランは必要ないため、クリーンなチャンバですぐに製品ウエハーを着工することができる。そのエッチングに1時間かかることは、従来装置と同じである。また、その1時間で、チャンバ内のリングと上部電極の内側に反応生成物が付着する。しかし、酸素プラズマを使ったWACにより、反応生成物を全て除去し、クリーンなチャンバに戻すことができる。そのため、2枚目以降の製品ウエハーも、常にクリーンなチャンバでメモリホールの開口を行うことができる。“チャンクリ”のために、毎日のようにチャンバを大気開放する必要はない。

ただし、アスペクト比40〜50を超えるようなHARC加工では、高エネルギーイオンを孔底に垂直にたたきつける必要があるため、エッチング条件を高真空かつ高バイアスにする必要がある(文献1の149〜153ページを参照した)。そのような過酷条件のエッチングであるため、エッジリングの消耗が激しい。筆者の調査によれば、従来装置のような“チャンクリ”は必要ないが、かなり高頻度でチャンバを大気開放して、エッジリングの交換を行わなくてならないと聞いていた。

Sense.iの登場と今後の製造装置の動向

このような3次元NANDのメモリホールの開口において、ドライエッチング装置が、消耗したエッジリングを自動で交換してくれるSense.iが登場した。このSense.iにより、3次元NANDの生産性は、飛躍的に向上するだろう。メモリメーカーにおいて、Sense.iを使っているか否かが、生産性やコストに大きく影響することになる。Lamは、TELなどの競合他社を大きく引き離したといえるだろう。

さらに、「装置が自動で消耗部品を交換する」という流れは、他の製造装置にも波及していくだろう。特に、CVD(化学気相成長)装置やスパッタ装置などの真空チャンバを必要とする装置は、極力、大気開放しないように、開発が加速すると考えられる。

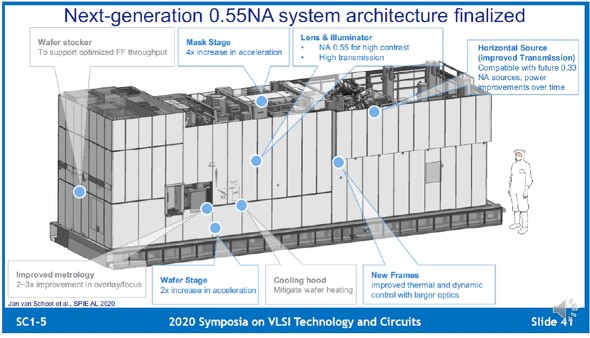

加えて、もう一つ忘れてはならないのが、最先端露光装置のEUVだ(図14)。EUVでは、露光に用いる波長13.5nmの光が空気中で減衰してしまうため、巨大な真空チャンバ内に反射レンズなどの光学系やマスクを収納している。従って、いったん、真空を破って大気開放すると、真空引きに多大な時間を要することになる。それ故、「装置が自動で消耗部品を交換する」機能が必要不可欠な装置といえよう。EUVがどのように進化していくかも注目の的である。

図14:最先端露光装置EUV(NA0.55) 出典:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5(クリックで拡大)

図14:最先端露光装置EUV(NA0.55) 出典:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5(クリックで拡大)素朴な疑問が画期的な創造を生む

筆者は、1987年に日立製作所に入社し、半導体技術者になった初期のころ、「同じプラズマ装置なのに、なぜドライエッチング装置でアッシングができないのだろう?」と疑問を持った。また、1995年に半導体事業部のDRAM工場に異動になった時は、「何で“チャンクリ”なんかしなくちゃならないんだろう?」と嘆いた(“チャンクリ”は工場デビューの新人に課せられた、できるならやりたくない仕事だった)。しかし、30代も半ばになりベテランの域に入ってしまうと、「ドライエッチングとはそういうものだ」ということが常識となり、疑問に思わなくなってしまった。

ところが、Lamは、筆者が抱いた素朴な疑問を追求し、チャンバ内部にリングを設置することによって、“チャンクリ”がほとんど必要なく、同一チャンバでエッチングとアッシングが可能になったドライエッチング装置を開発した訳である。

EE Times Japanの読者の中で、ビギナーの方がおられたら、その道に入った時の「違和感や疑問」を大切にして頂きたいと思う。もしかしたら、その素朴な「違和感や疑問」が画期的な創造を生み出す原動力になるかもしれないからだ。会社の中では、年上の諸先輩が、ビギナーの素朴な発想をたたきつぶすことが多いかもしれない。しかし、そんな年寄りのたわ言は、聞く必要は無い(といっている筆者も、もはや年寄りの部類に入るが、さて、あなたはどうする?)。

2020年11月10日 11:40に、本文について以下の通り修正を行っています。

1)「Cu/Low-kデュアルダマシン用エッチングにおいて東京エレクトロン(TEL)を凌駕する装置を開発し」

→「2000年代初旬にエッチングとアッシングの連続処理が可能なCu/Low-kデュアルダマシン用の画期的な装置を開発し」

2)「ゲート、メタル、絶縁膜、全てのドライエッチング装置の売上高シェアで、トップを快走している」

→「ゲート、メタル、絶縁膜、ドライエッチング装置の合計売上高シェアで、トップを快走している」

3)「なぜLamがHARCエッチング装置市場を独占しているのか?」

→「なぜLamが3次元NANDのメモリホール用装置を独占しているのか?」

4)「以下で、Cu/Low-kデュアルダマシン配線の形成プロセスについて説明する」

→「以下で2000年代初旬におけるCu/Low-kデュアルダマシン配線の形成プロセスについて説明する」

5)「このLamの絶縁膜ドライエッチング装置は、Cu/Low-kデュアルダマシン配線だけでなく、3次元NANDのメモリホールの開口にも必要不可欠な装置となっている。」

→「このような特徴を持つLamの絶縁膜ドライエッチング装置が、3次元NANDのメモリホールの開口に必要不可欠な装置となった。」

オンラインセミナー開催のお知らせ

2020年11月11日(水)、サイエンス&テクノロジー主催のセミナーにて、『コロナで変化が加速した世界半導体産業の《最新動向》 生きるか死ぬかを左右する知恵と情報の羅針盤』のタイトルで講演します。会場受講を15人に限定し、Live配信およびアーカイブ配信により、自宅や会社で受講できるようにしました。多くの皆さまのご参加をお待ちしております。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

関連記事

「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

Huaweiを取り巻く状況が、ますます厳しくなっている。米国による輸出規制の厳格化により、プロセッサだけでなく、CMOSイメージセンサーやメモリ、そしてパネルまでも調達が難しくなる可能性が出てきた。Huaweiが生き残る手段はあるのだろうか。 1nmが見えてきたスケーリング 「VLSI 2020」リポート

1nmが見えてきたスケーリング 「VLSI 2020」リポート

初のオンライン開催となった「VLSIシンポジウム 2020」から、スケーリング、EUV、3D ICの3つについて最新動向を紹介する。 中国は先端DRAMを製造できるか? 生殺与奪権を握る米国政府

中国は先端DRAMを製造できるか? 生殺与奪権を握る米国政府

2019年11月から12月にかけて、中国のメモリ業界に関して、驚くようなニュースが立て続けに報じられている。筆者が驚いた3つのニュース(事件と言ってもよいのではないか)を分析し、今後、中国が先端ロジック半導体や先端DRAMを製造できるか考察してみたい。 EUVスキャナー、出荷は堅調だが稼働率の課題も

EUVスキャナー、出荷は堅調だが稼働率の課題も

SEMI Japanは2020年8月25日、「第6回 SEMI Japanウェビナー」を開催した。今回のウェビナーにはASMLジャパンが登壇し、EUV(極端紫外線)リソグラフィ装置の最新状況を含めた同社の近況を報告した。 SiCパワー半導体用高温イオン注入装置、納入開始

SiCパワー半導体用高温イオン注入装置、納入開始

日新イオン機器は、SiC(炭化ケイ素)パワー半導体製造用高温イオン注入装置「IMPHEAT−II」の納入を始めた。従来装置に比べ、生産性が約3倍向上するという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- 加賀電子が新光商事にTOB、完全子会社化へ

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴